Файл: Задача данной выпускной квалификационной работы (далее вкр) состоит в том, что необходимо настроить совместную работу платы ацпцап data Conversion hsmc и плис cyclone iv e, установленной на отладочную плату de2115.docx

Добавлен: 09.11.2023

Просмотров: 180

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

6 Реализация проекта ПЛИС

6.1 Параметры опорного напряжения

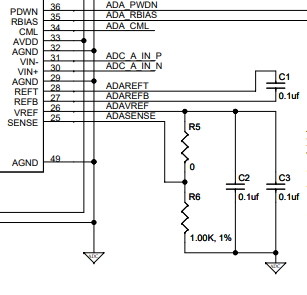

В разделе 3 данной ВКР изучались различные схемы подключения опорного напряжения к микросхеме AD9254. На плате Data Conversion HSMC используется та же схема, что и на рисунке 14. Для наглядности сходства этих схем подключения опорного напряжения на рисунке 35 представлена схема подключения опорного напряжения к микросхеме AD9254 на плате Data Conversion HSMC.

Рисунок 35 – Схема подключения опорного напряжения к микросхеме AD9254 на плате Data Conversion HSMC

При этой схеме подключения значения опорного напряжения будет составлять:

где

– номинал сопротивления резистора

– номинал сопротивления резистора  ;

; – номинал сопротивления резистора

– номинал сопротивления резистора  .

.Резистор

имеет сопротивление в 0 Ом и является перемычкой, резистор

имеет сопротивление в 0 Ом и является перемычкой, резистор  имеет сопротивление в 1 кОм. Подставив значения, получим:

имеет сопротивление в 1 кОм. Подставив значения, получим:

Определившись со значением опорного напряжения, теперь можно задать параметры аналогового сигнала.

6.2 Параметры аналогового сигнала

На основе того, что значение опорного напряжения составляет 0,5 В, значение амплитуды аналогового сигнала тоже должно составлять 0,5 В.

Т. к. частота дискретизации микросхемы AD9254 составляет 150 МГц, частота аналогового сигнала по теореме Котельникова не должна быть выше 75 МГц. Однако, на плате DE2-115 есть генератор тактовых импульсов, который может выдавать сигналы с максимальной частотой в 50 МГц. Поэтому, частота аналогового сигнала не должна превышать 25 МГц.

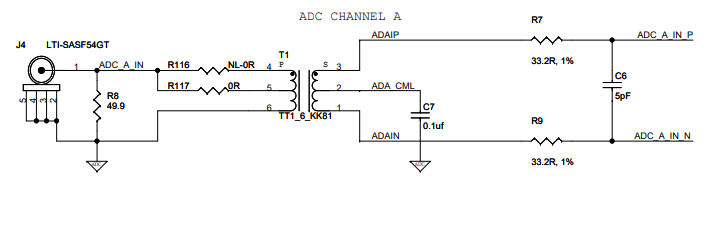

Однако, стоит сказать, что частота аналогового сигнала ограничивается не только сверху, но и снизу. В третьей главе мы уже рассматривали схемы подключения аналогового сигнала к микросхеме AD9254. На плате Data Conversion HSMC используется та же схема, что и на рисунке 9. Для наглядности сходства этих схем на рисунке 36 представлена схема подключения аналогового сигнала к микросхеме AD9254 на плате Data Conversion HSMC

Форма аналогового сигнала может быть любой. Но для начала подадим на микросхему AD9254 сигнал синусоидальной формы.

Рисунок 36 – Схема подключения аналогового сигнала к микросхеме AD9254 на плате Data Conversion HSMC

Из рисунка 36 видно, что на плату установлен трансформатор

TT1 6 KK81. Его характеристики представлены в таблице 15 [5].

Таблица 15 – Характеристики трансформатора TT1 6 KK81

| Параметр | Значение параметра |

| Соотношение первичной и вторичной обмоток | 1:1 |

| Диапазон рабочих частот | 0,004 – 300 МГц |

| Потери на входе | при частотах от 0,1 до 50 МГц: 1 дБ при частотах от 0,02 до 200 МГц: 2 дБ при частотах от 0,004 до 300 МГц: 3 дБ |

Исходя из того, что отношение первичной и вторичной обмотки трансформатора составляет 1:1, можно сделать вывод о том, что амплитуда сигнала не поменяется. Минимальная частота сигнала, судя по таблице 15. Должна составлять не менее 4 кГц.

Также, учитывая, что схема, представленная на рисунке 36, используется для преобразования сигнала в дифференциальный вид

Итого, параметры аналогового сигнала представлены в таблице 15.

Таблица 15 – Параметры аналогового сигнала

| Параметр сигнала | Значение |

| Амплитуда | 0,5 В |

| Частота | не более 25 МГц |

| Форма | синусоидальная |

Работа по реализации проекта ПЛИС будет вестись с микросхемой U1 (см. табл. 5), поэтому аналоговый сигнал будет вестись с SMA-разъема J4 через внешний генератор. Важно, чтобы выход генератор имел выходное сопротивление в 50 Ом.

6.3 Параметры тактовых импульсов

Согласно технической документации на плату DE2-115, генератор тактовых импульсов может выдавать сигналы с максимальной частотой в 50 МГц. Для наилучшего преобразования сигнала будет использоваться частота в 50 МГц.

Сигналы тактовых импульсов имеют форму LVDS (дифференциального сигнала). Размах сигнала по напряжению составляет 3,3 В.

Итого, параметры тактовых импульсов представлены в таблице 16.

Таблица 16 – Параметры тактовых импульсов

| Параметр сигнала | Значение |

| Размах сигнала | 3,3 В |

| Частота | 50 МГц |

| Форма | дифференциальная |

Тактовые импульсы подаются через HSMC-разъем через

контакты 95 и 97.

Чтобы подать тактовые импульсы, необходимо соединить между собой контакты 3-5 и 4-6 на перемычке J3.

6.4 Назначение контактов HSMC-разъема

HSMC-разъем содержит в себе 172 контакта. Однако, для начала нужно проверить, сможет ли плата DE2-115 принять хоть какие-нибудь данные из платы Data Conversion HSMC. Поэтому для начала будет проверен тестовый проект ПЛИС с синхронизированной ОЗУ.

Для проверки тестового проекта ПЛИС потребуются контакты:

-

для вывода преобразованных данных с АЦП; -

с контакта АЦП OR (для оценки выхода за пределы измерений); -

с контакта АЦП OE (для разрешения вывода данных).

В таблице 17 представлено назначение контактов для тестового проекта ПЛИС

Таблица 17 – Назначение контактов HSMC-разъема для тестового проекта ПЛИС

| Номер контакта | Назначение контакта | Адрес контакта для ПЛИС |

| 79 | Вывод бита D0 (младший бит) | PIN_M28 |

| 77 | Вывод бита D1 | PIN_M27 |

| 73 | Вывод бита D2 | PIN_K28 |

| 71 | Вывод бита D3 | PIN_K27 |

Продолжение таблицы 17

| Номер контакта | Назначение контакта | Адрес контакта для ПЛИС |

| 67 | Вывод бита D4 | PIN_G28 |

| 65 | Вывод бита D5 | PIN_G27 |

| 61 | Вывод бита D6 | PIN_F28 |

| 59 | Вывод бита D7 | PIN_F27 |

| 55 | Вывод бита D8 | PIN_E28 |

| 53 | Вывод бита D9 | PIN_E27 |

| 49 | Вывод бита D10 | PIN_D28 |

| 47 | Вывод бита D11 | PIN_D27 |

| 43 | Вывод бита D12 | PIN_AE27 |

| 41 | Вывод бита D13 (старший бит) | PIN_AE26 |

| 156 | Тактовый импульс для вывода данных (DCO) | PIN_Y27 |

| 83 | Выход за пределы измерений (OR) | PIN_K21 |

| 85 | Разрешение на вывод данных (OE) | PIN_K22 |

| 95 | Подача тактовых импульсов на АЦП (CLK+) | PIN_G23 |

| 97 | Подача тактовых импульсов на АЦП (CLK-) | PIN_G24 |

6.7 Проверка тестового проекта ПЛИС

Сначала была проведена настройка плат DE2-115 и Data Conversion HSMC.

На перемычке JP3 на плате Data Conversion HSMC были установлены соединители в положение 3-5 и 2-4 для выбора источников тактовых импульсов для АЦП (см. табл. 1).

На перемычке JP7 на плате DE2-115 соединители были установлены в положение 7-8.

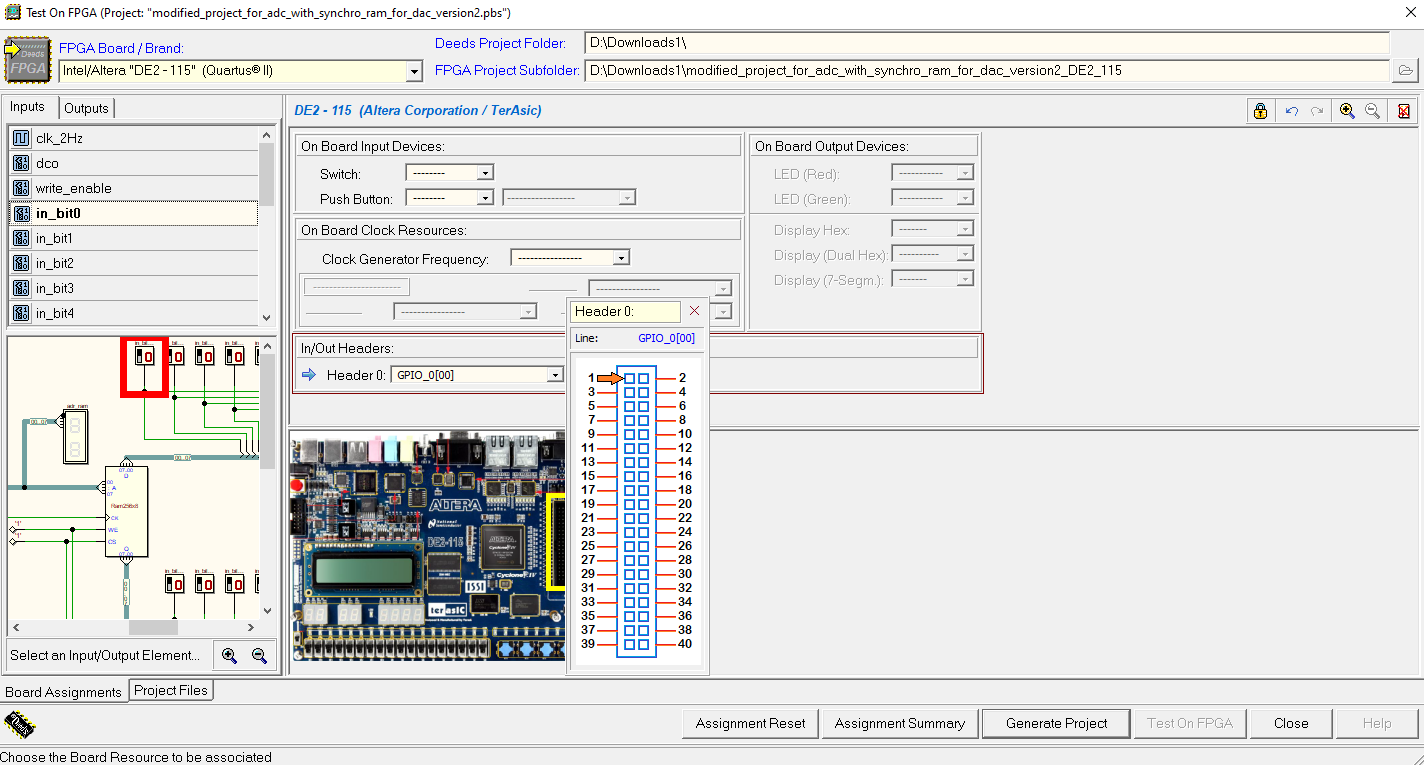

Далее в среде разработки DEEDS было проведено назначение элементов, как это показано на рисунке 37.

Рисунок 37 – Назначение элементов в среде разработки DEEDS

Из рисунка 37 видно, что ПО DEEDS не поддерживает назначение элементов через HSMC-разъем. Поэтому все вводы и выводы, относящиеся к HSMC-разъему, были назначены на GPIO-разъем для дальнейшей успешной загрузки проекта. Если эти вводы и выводы не назначить на GPIO-разъем, то ПО DEEDS не даст перейти в ПО Quartus Prime и загрузить проект в ПЛИС.

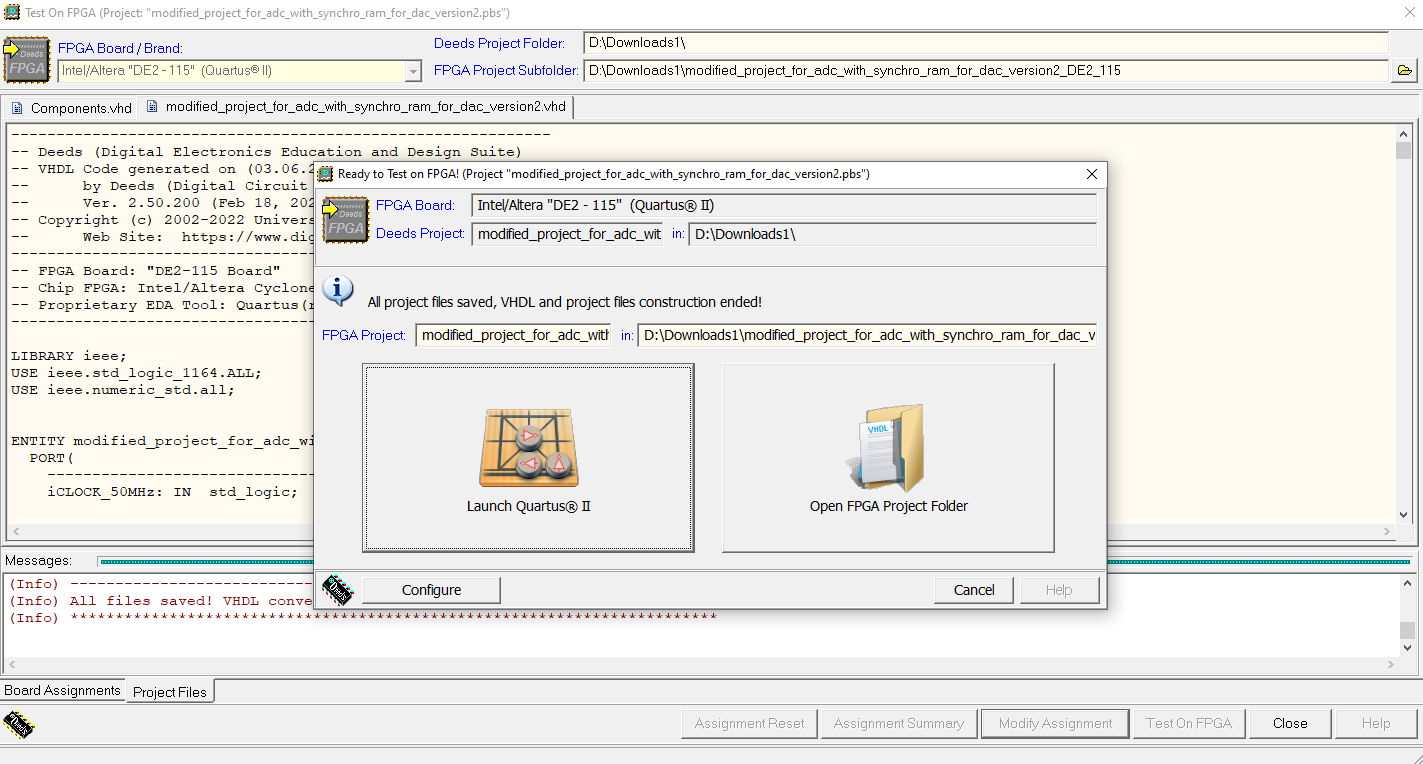

После назначения вводов и выводов к GPIO-разъему ПО DEEDS сформировала проект ПЛИС на языке программирования VHDL и далее предложило перейти в среду разработки Quartus Prime (см. рис. 38).

Рисунок 38 – Формирование проекта ПЛИС на языке программирования VHDL

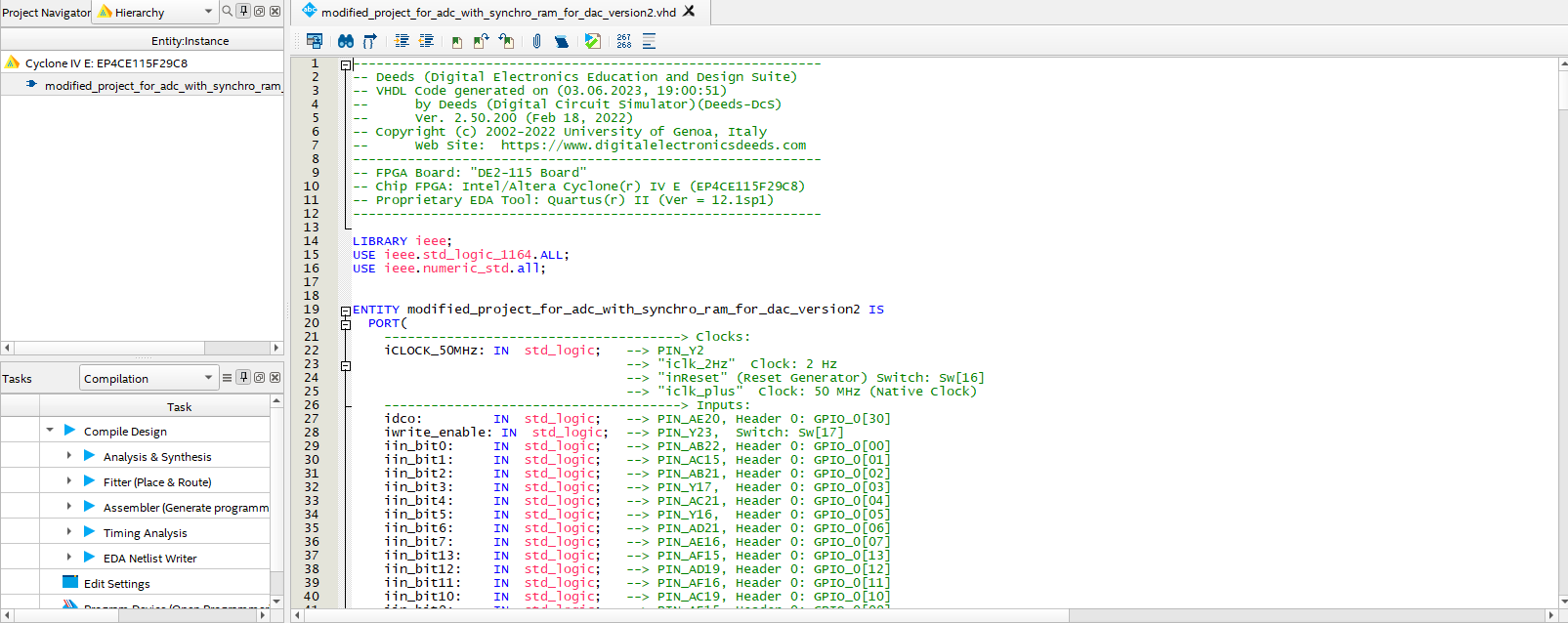

Далее отрылось окно среды разработки Quartus Prime, где уже был открыт проект ПЛИС и была произведена корректировка кода. В коде корректировались адреса для назначения вводов и выводов в соответствии с таблицей 17 (см. рис. 39).

Рисунок 39 – Корректировка кода в среде Quartus Prime

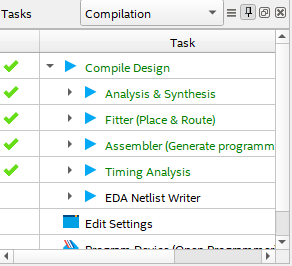

После этого был запущен процесс компиляции проекта ПЛИС. Результаты компиляции представлены на рисунке 39.

Рисунок 39 – Результаты компиляции тестового проекта ПЛИС

Из рисунка 39 видно, что тестовый проект ПЛИС успешно прошел все стадии компиляции.

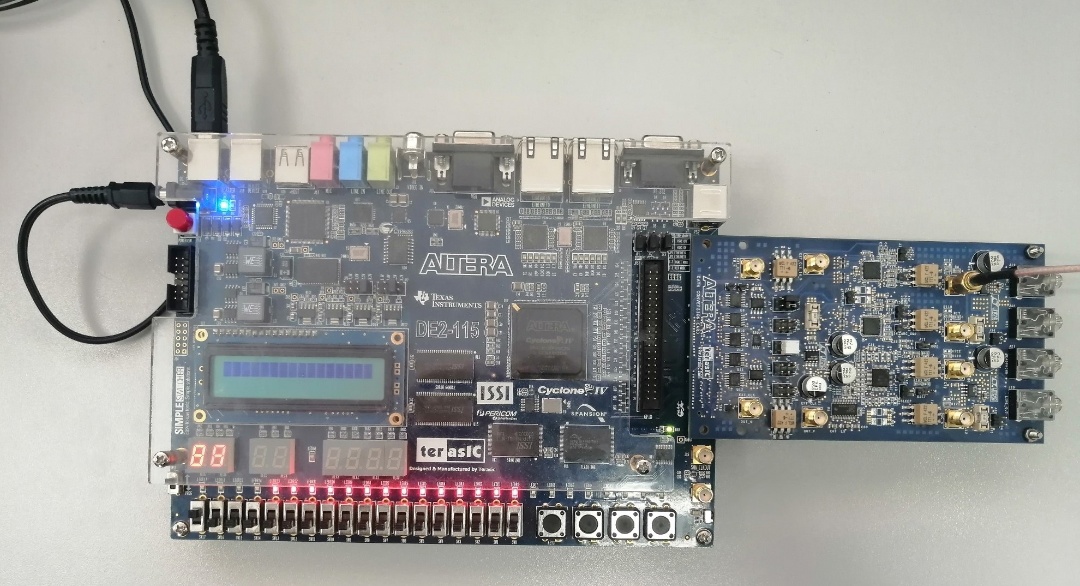

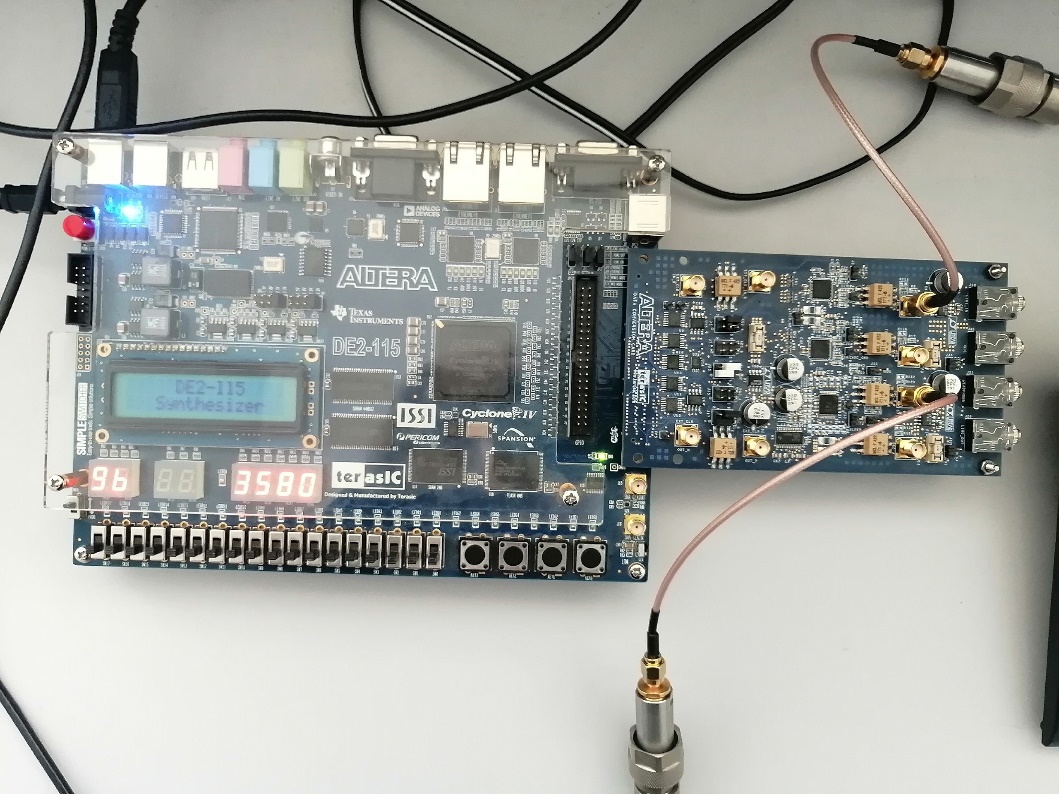

Далее проект был загружен в ПЛИС. На тот момент плата Data Conversion HSMC уже была подключена к плате DE2-115, к SMA-разъему J4 был подключен генератор сигналов (см. рис. 40).

Рисунок 40 – Подключенные платы DE2-115 и Data Conversion HSMC

После загрузки проекта на ПЛИС переключатель SW17 был переключен в «верхнее» положение для того, чтобы разрешить ячейкам ОЗУ запись данных с АЦП.

Затем этот переключатель был переключен в «нижнее» положение. Запись данных с АЦП запрещается в этот момент, и ОЗУ переходит в режим чтения. На рисунке 41 представлены результаты записи данных с АЦП.

Рисунок 41 – Результаты записи данных с АЦП

Из рисунка 41 видно, что красные светодиоды LEDR0 – LEDR13 постоянно горят красным цветом. Это означает, что на них постоянно приходят логические единицы. Такая ситуация наблюдалась при переключении всех адресов ячеек ОЗУ. При синусоидальной форме сигнала такого быть не должно.

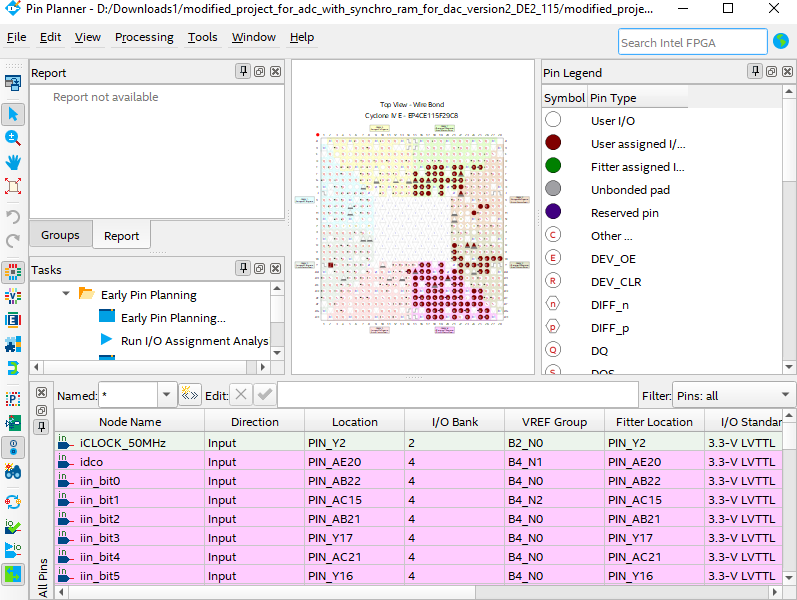

Проблема была связана с тем, что экспортируемый проект ПЛИС на языке программирования VHDL не поддерживает назначение вводов и выводов на HSMC-разъем. Поэтому адреса вводов и выводов из HSMC-разъема пришлось назначать вручную с помощью инструмента Pin Planner в среде разработки Quartus Prime.

Назначение вводов и выводов в инструменте Pin Planner представлено на рисунке 42.

Рисунок 42 – Назначение вводов и выводов в инструменте Pin Planner

После этого проект снова пришлось проверить с помощью компиляции и заново загрузить на ПЛИС. Результаты работы ПЛИС представлены на рисунке 43.

Рисунок 43 – Работа ПЛИС после переназначения вводов и выводов

Из рисунка 43 видно, что ПЛИС теперь принимает сигналы от АЦП более корректно. При обращении к ячейкам ОЗУ на семи-сегментных индикаторах постоянно выводились разные значения.

6.8 Проверка проекта ПЛИС с подключением к ЦАП

Далее была проведена проверка проекта ПЛИС с подключенным к ней ЦАП. Схема проекта уже была ранее представлена на рисунке 34. Назначение контактов HSMC-разъема для данного проекта представлено в приложении В.

Как и в случае с тестовым проектом, возникла проблема назначения вводов и выводов. Пришлось также назначать их с помощью инструмента

Pin Planner. Проект также прошел после этого успешную компиляцию и был загружен в ПЛИС.

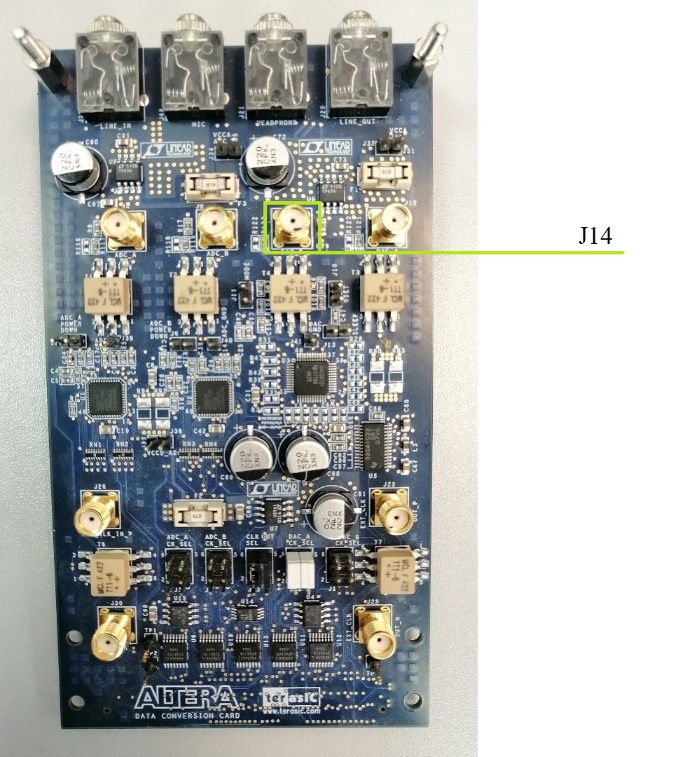

К SMA-разъему J14 на плате Data Conversion HSMC был подключен коаксиальный кабель для отображения оцифрованного сигнала на осциллографе. Расположение SMA-разъема J14 показано на рисунке 44.