ВУЗ: Казахская Национальная Академия Искусств им. Т. Жургенова

Категория: Книга

Дисциплина: Не указана

Добавлен: 03.02.2019

Просмотров: 21737

Скачиваний: 19

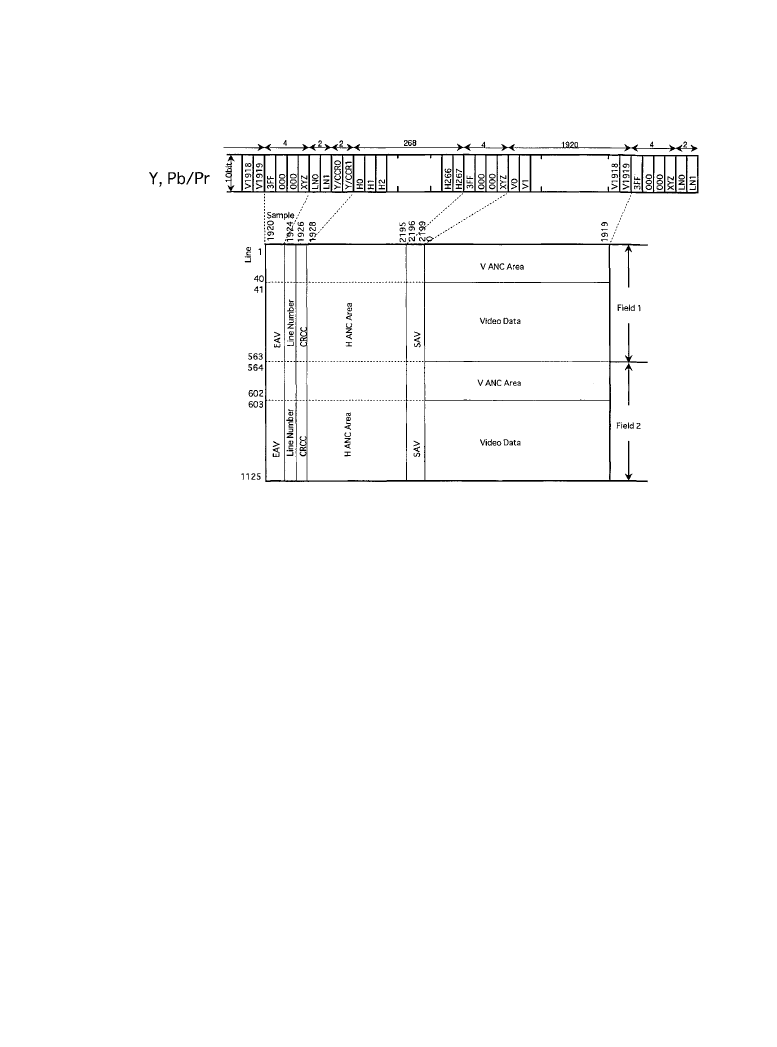

8-18 Audio Networking

The video clock frequency is 74.25 MHz (or 74.25/1.001 MHz), which is synchronous with

the video data. The audio data packet is multiplexed in the HANC area of the chrominance chan-

nel, with the exception of lines 8 and 570. All of the video and ancillary data present in the input

digital signal, and the embedded data (line numbers, EAV/SAV, CRC, and other data) are trans-

mitted to the P/S device without alteration, where the data is converted into a serial form. Figure

8.2.4 shows the data footprint for the system.

As mentioned previously, the interface between the coprocessor and P/S converter consists of

two channels of I/O bit parallel data at 74.25 Mwords/s. The P/S IC converts these two parallel

channels into a serial data stream at 1.485 Gbits/s by means of a 20-to-1 multiplexer. This serial

data is then encoded using scrambled NRZI. The generator polynomial for the NRZI scrambler is

[4]:

(8.2.1)

From the P/S IC, the encoded serial data is output in ECL form and distributed by 3 channels

of coaxial outputs. The signal amplitude of the coaxial output is 800 mV p-p into 75

Ω.

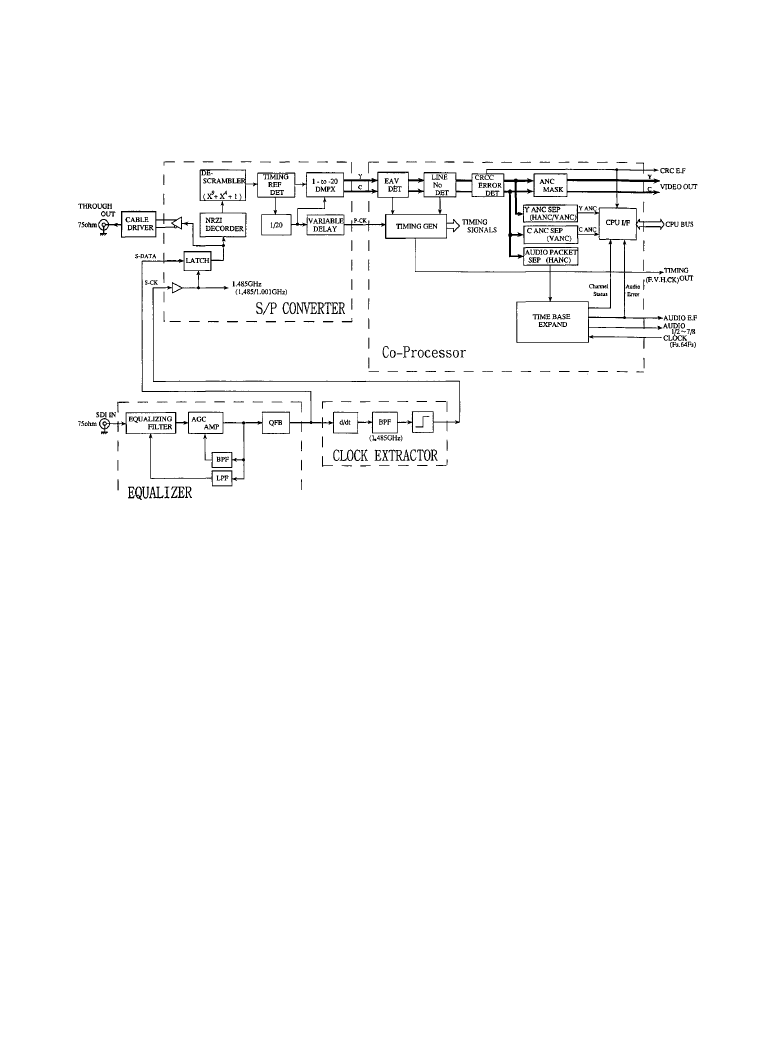

Figure 8.2.5 shows a block diagram of the receiver module. Cable equalizer circuitry compen-

sates for high-frequency losses of the coaxial cable, and the clock recovery circuit extracts the

G

x

( )

x

9

x

4

1

+

+

(

)

x

1

+

(

)

⋅

=

Figure 8.2.4

The HD-SDI signal format from the coprocessor IC to the P/S device. (

From [4].

Courtesy of Sony.)

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com)

Copyright © 2004 The McGraw-Hill Companies. All rights reserved.

Any use is subject to the Terms of Use as given at the website.

Serial Digital Video/Audio Systems

Serial Digital Video/Audio Systems 8-19

1.485 GHz serial clock. The serial-to-parallel converter section reconstructs the parallel data

from the serial bitstream, while the coprocessor IC separates the video, audio, and ancillary data.

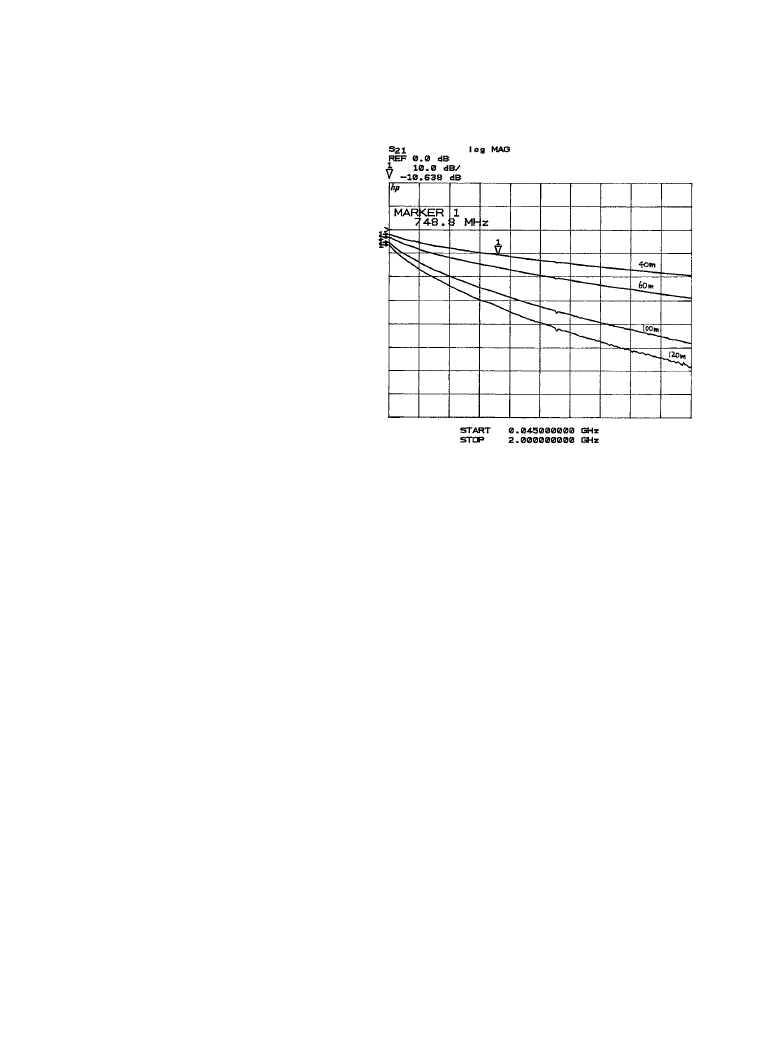

The cable equalizer is an automatic system that compensates for the frequency-dependent atten-

uation of coaxial cable. The attenuation characteristic of a 5C-2V cable (75

Ω, comparable to

Belden 8281) is shown in Figure 8.2.6.

By using a PIN diode, the compensation curve of the receiving system can be controlled

while satisfying the condition of linear phase. The cable length is detected by a band-pass filter,

and the equalizing filter is controlled to keep the amplitude constant. A dc restorer also is used.

After a decision stage, the threshold-controlled signal is fed back through a low-pass filter, per-

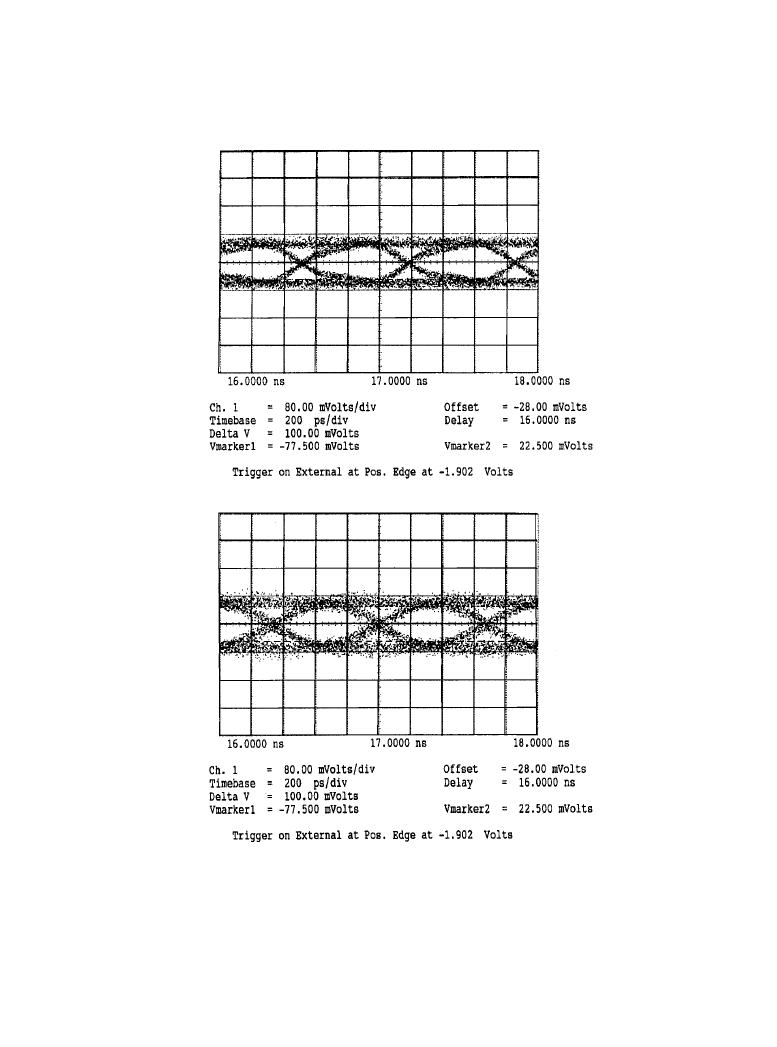

mitting recovery of the dc component. The data given in Figure 8.2.7 show the eye-patterns for

two cable lengths. The bit error rate for 1.485 Gbits/s transmission over these lengths is less than

1 error in 10

10

.

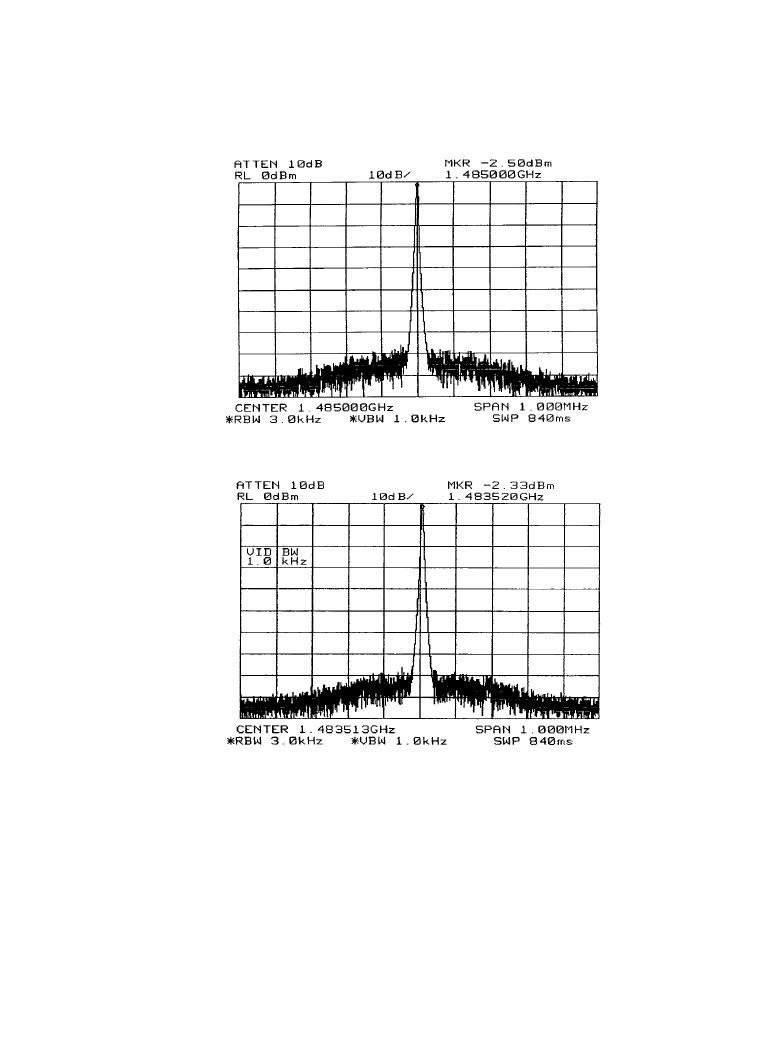

The clock recovery circuit is a clock frequency filter that works on the serial data recovered

from the cable equalizer. The transition edges of the serial data contain the 1.485 GHz clock fre-

quency that is selected by the filter. The HDTV source formats make use of two field frequen-

cies: 60.00 Hz and 59.94 Hz. Hence, the HD-SDI system provides two values for the serial clock

frequency, that is, 1.485 GHz and 1.4835 GHz (1.485 GHz/1.001). Figures 8.2.8a and 8.2.8b

show the recovered clock frequencies of 1.485 GHz and 1.4835 GHz, respectively.

The serial-to-parallel converter reconstructs the parallel data from the serial bit stream. The

serial data recovered from the cable equalizer is reclocked by the serial clock frequency that is

Figure 8.2.5

Block diagram of an HD-SDI receiver system. (

From [4]. Courtesy of Sony.)

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com)

Copyright © 2004 The McGraw-Hill Companies. All rights reserved.

Any use is subject to the Terms of Use as given at the website.

Serial Digital Video/Audio Systems

8-20 Audio Networking

produced at the output of the clock recovery circuit. At this point, the channel coding scrambled

NRZI is decoded and the unique pattern of the timing reference signal EAV/SAV is detected. In

order to generate the 74.25 MHz clock frequency for the parallel data words, the 1.485 GHz

serial clock is divided by 20 and synchronized using detection of the timing reference signals.

The serial data is next latched by the parallel clock waveform to generate the 20 bits of parallel

data. The serial data, latched by the serial high-frequency clock, also is provided as an active

loop-through output.

The coprocessor IC separates video, audio, and ancillary data from the 20-bit parallel digital

signal. EAV/SAV information and line number data are detected from the input signal, permit-

ting the regeneration of F/V/H video timing waveforms. Transmission errors are detected by

means of CRC coding.

The embedded audio packet is extracted from the HANC space of the P

B

/P

R

channel and the

audio data are written into memory. The audio data are then read out by an external audio clock

frequency F

s

, enabling the reconstruction of the received audio information. The coprocessor IC

can receive up to 8 channels of embedded audio data.

8.2.3b

Audio Interface Provisions

SMPTE 299M-1997 defines the mapping of 24-bit AES digital audio data and associated control

information into the ancillary data space of a serial digital video stream conforming to SMPTE

292M [6]. The audio data are derived from ANSI S4.40, more commonly referred to as AES

audio.

An audio signal, sampled at a clock frequency of 48 kHz locked (synchronous) to video, is

the preferred implementation for intrastudio applications. As an option, this standard supports

AES audio at synchronous or asynchronous sampling rates from 32 kHz to 48 kHz. The number

Figure 8.2.6

Attenuation charac-

teristics of 5C-2V coaxial cable.

(

From [4]. Courtesy of Sony.)

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com)

Copyright © 2004 The McGraw-Hill Companies. All rights reserved.

Any use is subject to the Terms of Use as given at the website.

Serial Digital Video/Audio Systems

Serial Digital Video/Audio Systems 8-21

(

a)

(

b)

Figure 8.2.7

Eye diagram displays of transmission over 5C-2V coaxial cable: (

a) 3 m length, (b)

100 m length. (

After [4]. Courtesy of Sony.)

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com)

Copyright © 2004 The McGraw-Hill Companies. All rights reserved.

Any use is subject to the Terms of Use as given at the website.

Serial Digital Video/Audio Systems

8-22 Audio Networking

of transmitted audio channels ranges from a minimum of two to a maximum of 16. Audio chan-

nels are transmitted in pairs, and where appropriate, in groups of four. Each group is identified

by a unique ancillary data ID.

(

a)

(

b)

Figure 8.2.8

Recovered signal clocks: (

a) 1.485 GHz 60 Hz system, (b) 1.4835 GHz 59.94 Hz

system. (

After [4]. Courtesy of Sony.)

Downloaded from Digital Engineering Library @ McGraw-Hill (www.digitalengineeringlibrary.com)

Copyright © 2004 The McGraw-Hill Companies. All rights reserved.

Any use is subject to the Terms of Use as given at the website.

Serial Digital Video/Audio Systems