Файл: Проектирование цифрового арифметикологического устройства на интегральных микросхемах.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.11.2023

Просмотров: 86

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Расчет быстродействия схемы заключается в определении задержки распространения сигнала с того момента, как нажата кнопка “Равно”, и до момента появления результата вычисления на индикаторах. Для расчёта быстродействия необходимо определить самый длинный путь прохождения сигнала в проектируемом устройстве. В данном случае самый длинный путь при выполнении арифметической операции вычитание. Путь быстродействия имеет следующий вид:

-

Входные буферы.

tbuf = 17 нс

-

Схема вычитания.

Прохождение по схеме 32-разрядного вычитания состоит из 2 шагов. Первый шаг – прохождение инвертирующих вентилей для операнда “B” (tnot= 7 нс) Второй шаг – прохождение схемы полного сумматора, в котором на каждую ступень полусумматора, приходится 17 нс (thalf_adder= 17 нс) и дополнительный вентиль OR (tor= 17 нс)

tsub = 7 + 17 х 3 = 58 (нс)

-

Выходные буферы.

tbuf = 17 нс

Итого суммарная задержка, начиная с нажатия клавиши равно и по получения результата на индикаторах равна:

Таблица 2.2. Подсчет итоговой задержки.

| Схема | Суммарная задержка, нс. |

| Входные буферы | 10 |

| Схема вычитания | 58 |

| Выходные буферы | 10 |

| Всего: | 78 |

Исходя из полученного значения временной задержки в 78 нс, можно сделать вывод о том, что разработанная схема полностью соответствует требованию по быстродействию в 100 нс. Дополнительных изменений схемы не требуется.

-

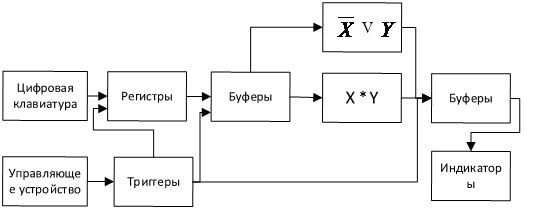

Структурная схема

Рисунок 2.30. Структурная схема в программе Microsoft Visio

-

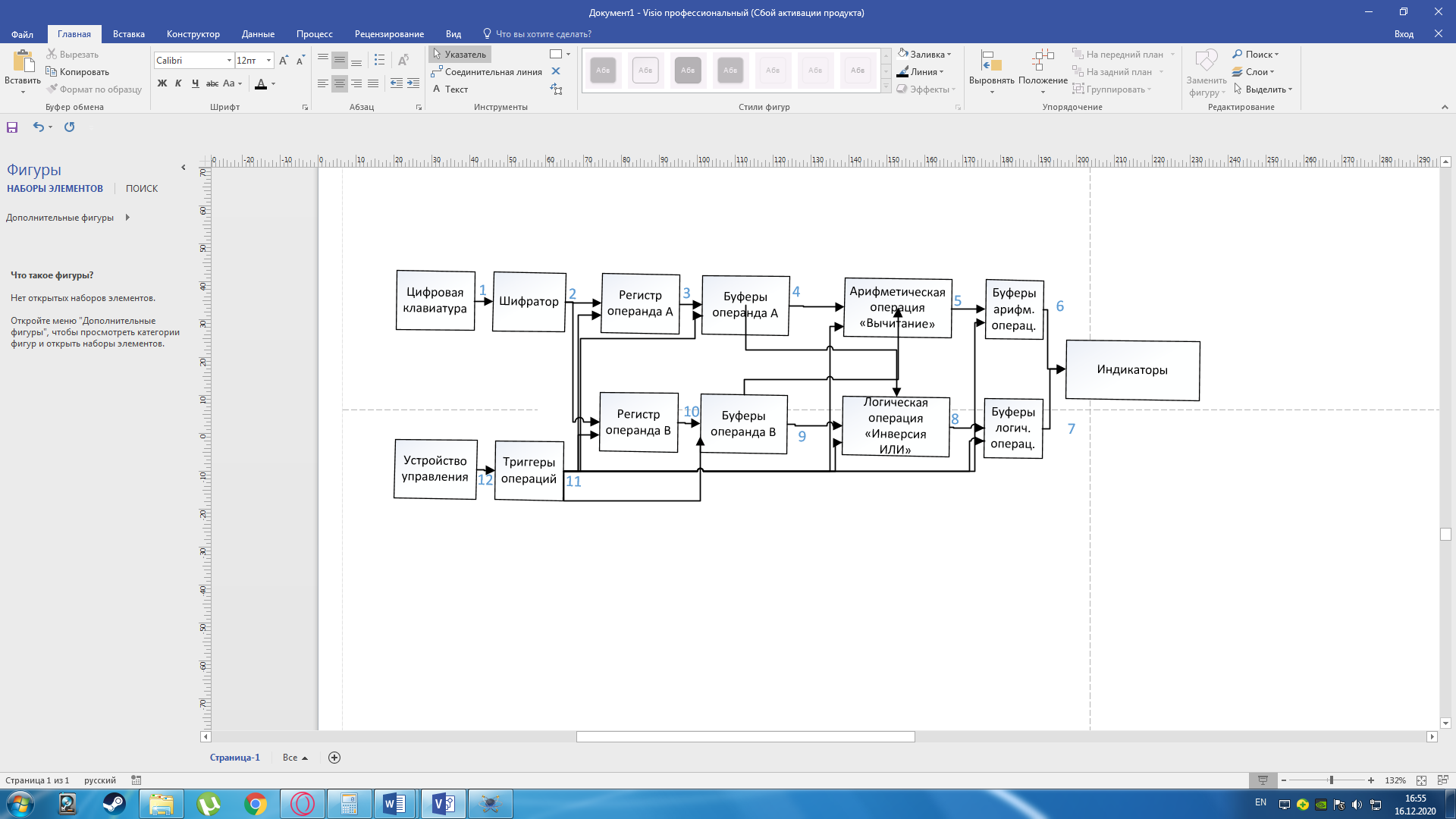

Функциональная схема

Функциональная схема

Рисунок 2.31. Функциональная схема в программе Microsoft Visio

Принципиальная схема

Принципиальная схема

Рисунок 2.32. Принципиальная схема в программе Proteus

Таблица 2.3. Обозначение связей на функциональной схеме:

| Номер | Значение |

| 1 | Унарный код цифры |

| 2 | Двоичный код цифры |

| 3 | Двоичный код цифры A |

| 4 | Двоичный код цифры A |

| 5 | Результат арифметической операции «Вычитание» в двоичном коде |

| 6 | Результат арифметической операции «Вычитание» в двоичном коде |

| 7 | Результат логической операции « |

| 8 | Результат логической операции « |

| 9 | Двоичный код цифры B |

| 10 | Двоичный код цифры B |

| 11 | Управляющие сигналы, равно, сброс, «Умножение», « |

| 12 | Управляющие сигналы, равно, сброс, «Умножение», « |

-

Заключение

В результате выполнения курсового проекта было реализовано цифровое арифметико-логическое устройство, позволяющее выполнять арифметическую операцию вычитания и логическую инверсию ИЛИ над 32-х разрядными операндами, представленными в шестнадцатеричной системе счисления. Были проведены работы по выборке подходящих микросхем, вычислению необходимых расчётов и проектированию самого устройства.

Схема устройства имеет возможность сброса регистров операндов и результата, для многократного выполнения арифметико-логических операций

Вычислительное устройство требует 2 мВт мощности при ограничении на потребляемую мощность в 300 мВт. Задержка распространения сигналов равна 78 нс. при ограничении в 300 нс. Таким образом схема полностью соответствует требованиям, указанным в задании.

-

Список использованной литературы

-

Хоровиц П., Хилл У. Искусство схемотехники: В 2-х томах = The Art of Electronics: Second Edition (© Cambridge University Press, 1980) / Пер. с англ. под ред. М. В. Гальперина, редакторы: Н. В. Серегина, Ю. Л. Евдокимова. — М.: Мир, 1983. — т. 1: 568 с., т. 2: 590 с. — 50 000 экз. -

Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т. 5 —М.; КУбК-а,1997г. —608 с: ил. -

Титце У., Шенк К. Полупроводниковая схемотехника. 12 е изд. Том II: Пер. с нем. – М.: ДМК. Пресс. – 942 с.: -

Угрюмов Е. П. У27 Цифровая схемотехника: Учеб. пособие для вузов. — 2-е изд., перераб. и доп. — СПб.: БХВ-Петербург, 2007. — 800 с.: ил. -

Методические указания к выполнению КП по схемотехнике «Проектирование цифровых устройств».

Приложение 1. Блок «Вычитание»

Приложение 1. Блок «Вычитание»

Приложение 2. Блок «

Приложение 2. Блок «