Файл: Проектирование цифрового арифметикологического устройства на интегральных микросхемах.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.11.2023

Просмотров: 90

Скачиваний: 4

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Расчет количества микросхем

Расчет количества необходимых микросхем проводился, например, для блока вычитания, следующим образом: полный сумматор использует 2 вентиля XOR, 2 вентиля AND и один вентиль OR. Всего блоков полных сумматоров 32, по количеству разрядов операндов. Получается, что блоков XOR, как и AND используется 2 х 32, т.е. 64. А вентилей OR 32. Микросхема КР 1564 ЛИ1, к примеру, имеет в своем составе 4 вентиля “И”. Следовательно, микросхем КР 1564 ЛИ1 нам потребуется 64 / 4, т.е. 16. То же справедливо и для остальных микросхем.

Расчетное количество микросхем, их мощности и быстродействия приведены в таблице 2.1.

-

Сводная таблица по микросхемам

Таблица 2.1. Наименования и количество использованных в курсовой работе микросхем.

| Название | Наименование | Зарубежный аналог | Количество использованных схем | Потребляемая мощность одного элемента, мкВт | Быстродействие, нс | |||

| На общей схеме | В блоках | Всего | ||||||

| Инверсия ИЛИ | Вычитание | |||||||

| Восьмиразрядный регистр на D триггерах с общим сбросом | КР 1564 ИР23 | 74HC273 | 8 | - | - | 8 | 48 | 18 |

| Двунаправленный инвертирующий буфер | КР 1564 АП3 | 74HC245 | 8 | 4 | 4 | 16 | 48 | 10 |

| Приоритетный шифратор 8 на 3 | КР 1564 ИВ1 | 74HC148N | 2 | - | - | 2 | 24 | 36 |

| 4 RS триггера | КР 1564 ТР2 | 74HC279 | 1 | - | - | 1 | 12 | 7 |

| | | | | | | | | |

| 6 элементов НЕ | КР 1564 ЛН1 | 74HC04 | 2 | 6 | 6 | 14 | 12 | 7 |

| 4 элемента ИЛИ | КР 1564 ЛЛ1 | 74HC32 | 4 | 8 | 8 | 20 | 12 | 17 |

| 4 элемента И | КР 1564 ЛИ1 | 74HC08 | 1 | - | 16 | 17 | 12 | 17 |

| 4 элемента исключающее ИЛИ | КР 1564 ЛП5 | 74HC86 | - | - | 16 | 16 | 12 | 20 |

- 1 2 3 4 5 6 7 8

Характеристики микросхем

-

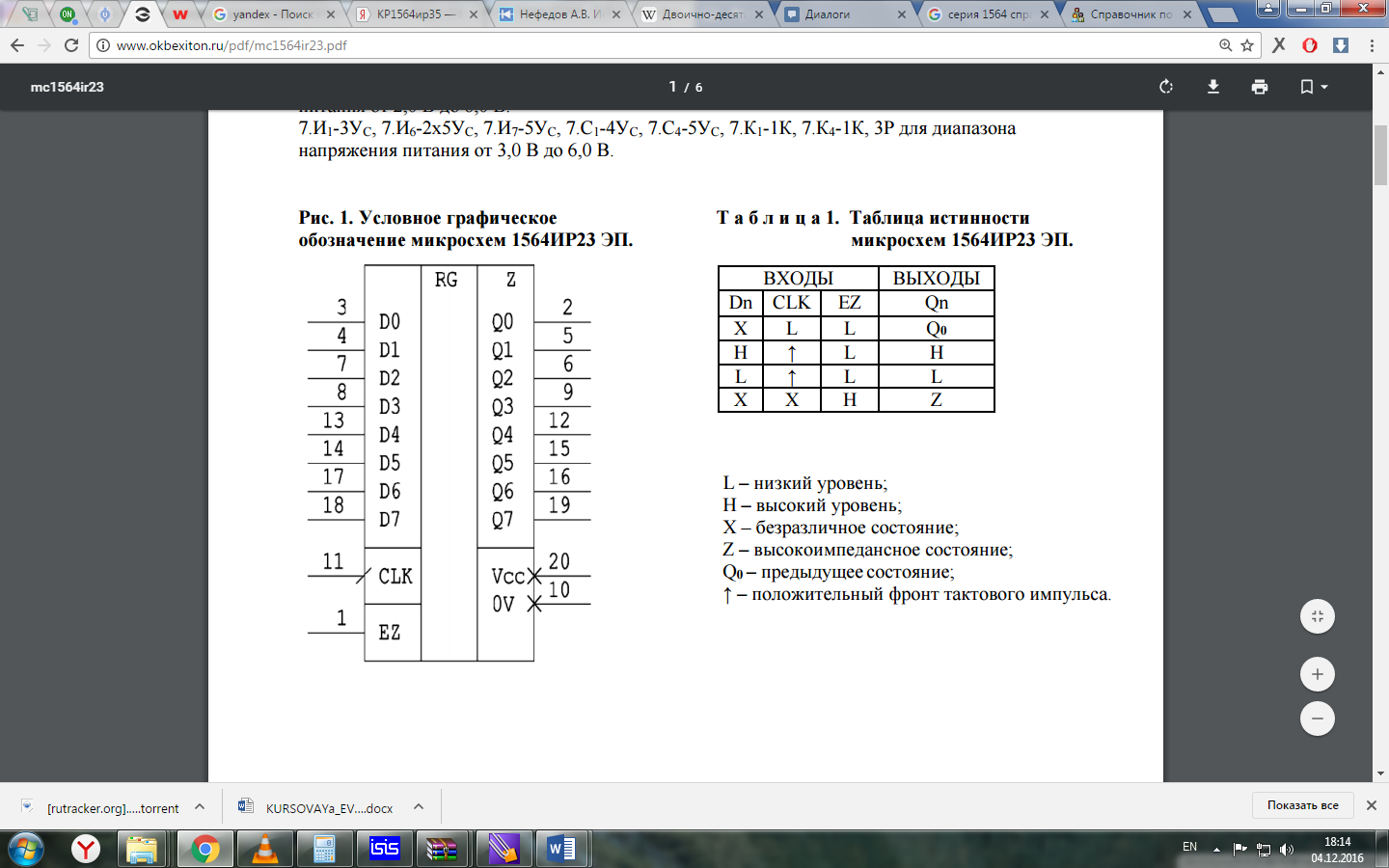

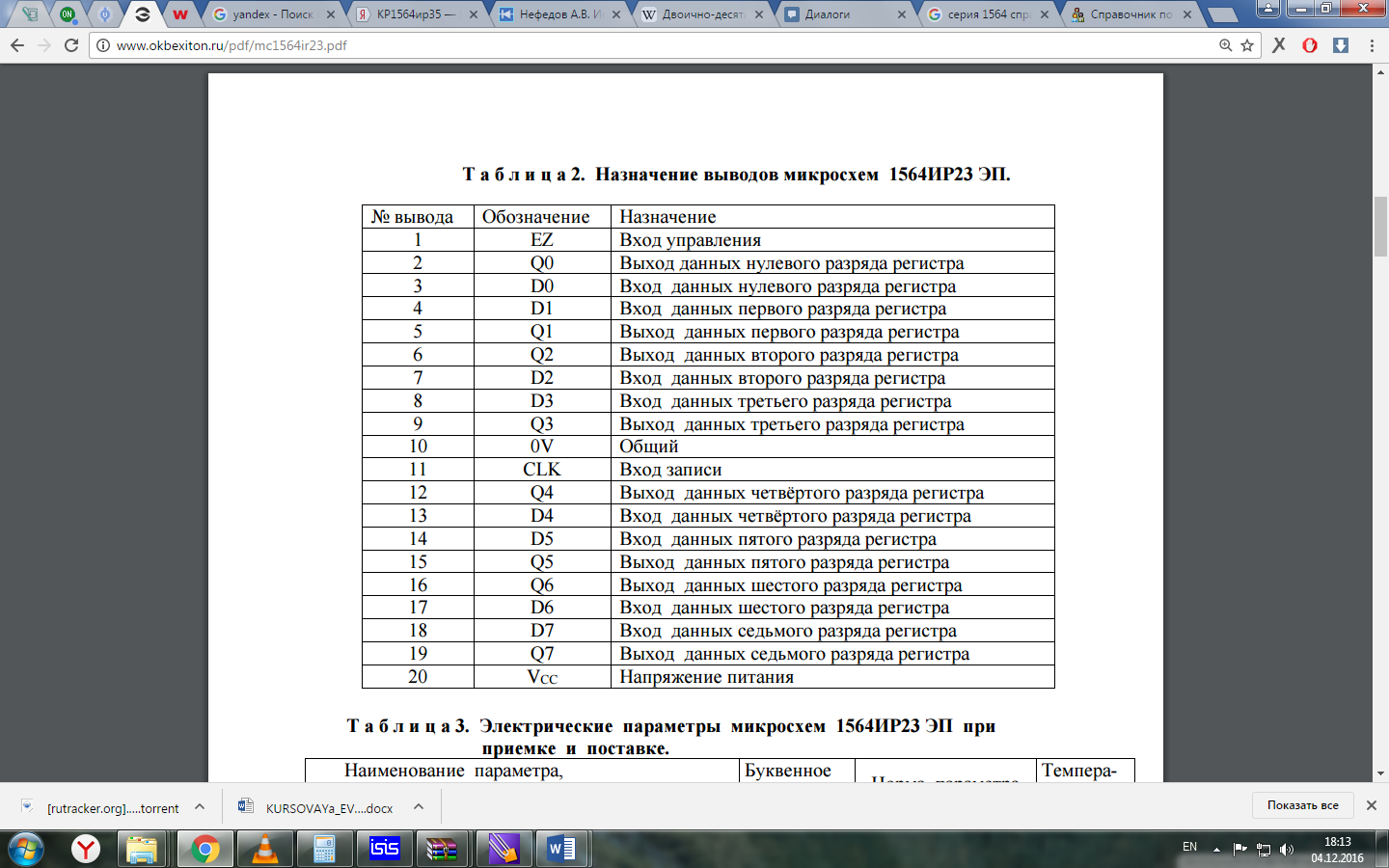

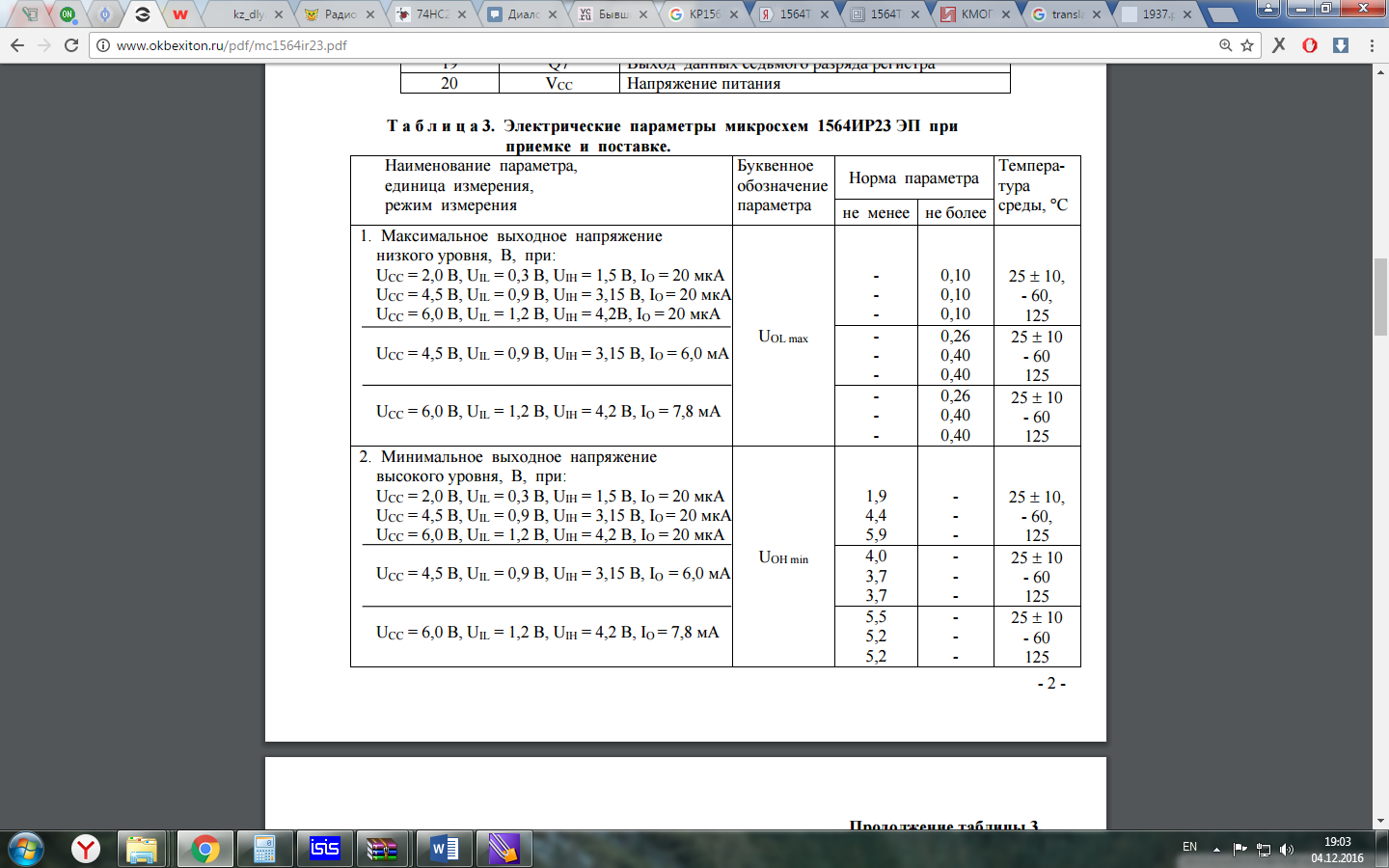

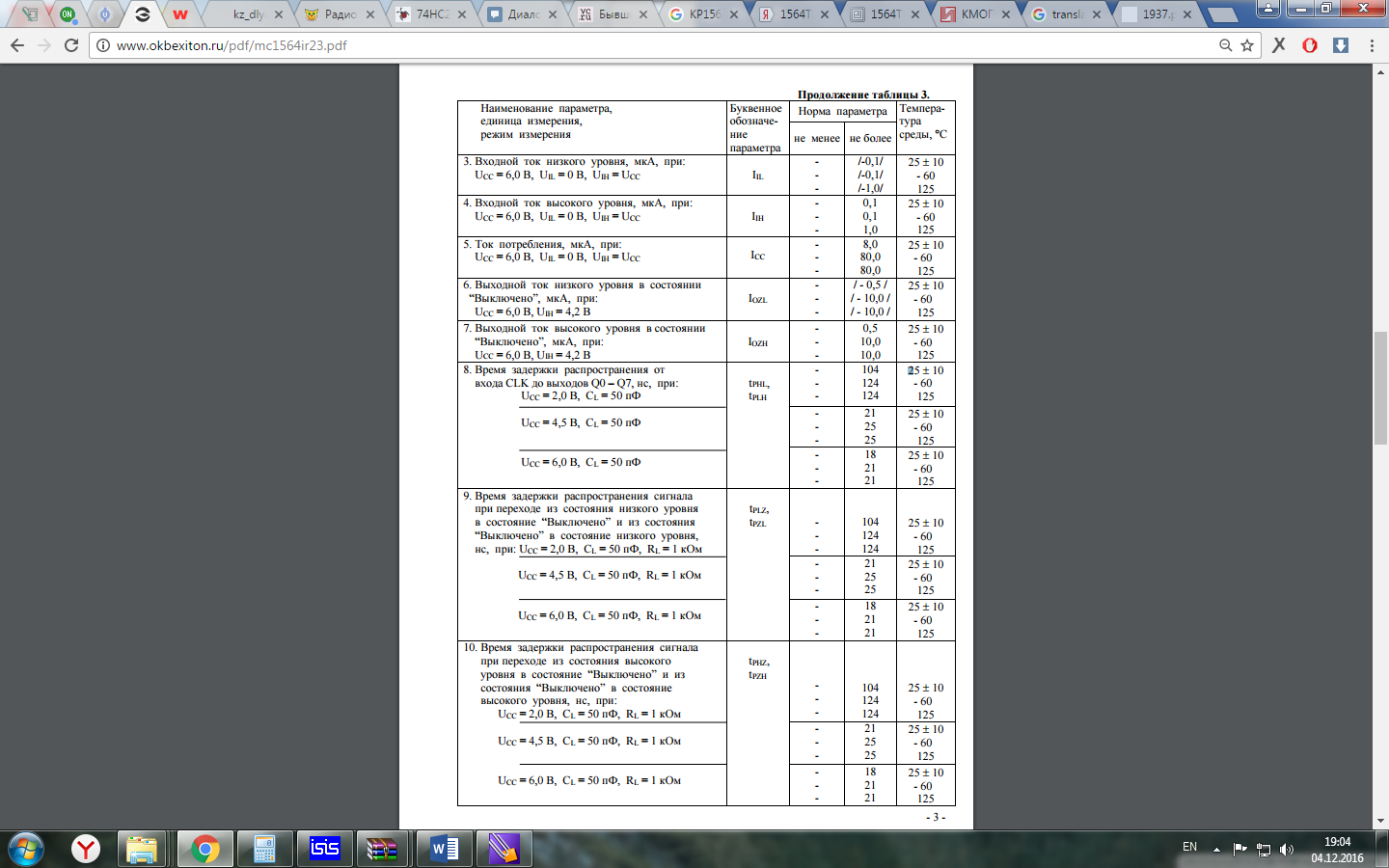

Восьмиразрядный регистр на D триггерах с общим сбросом (КР 1564 ИР23)

Рисунок 2.13. Условное графическое обозначение, таблица истинности и назначения выводом микросхем

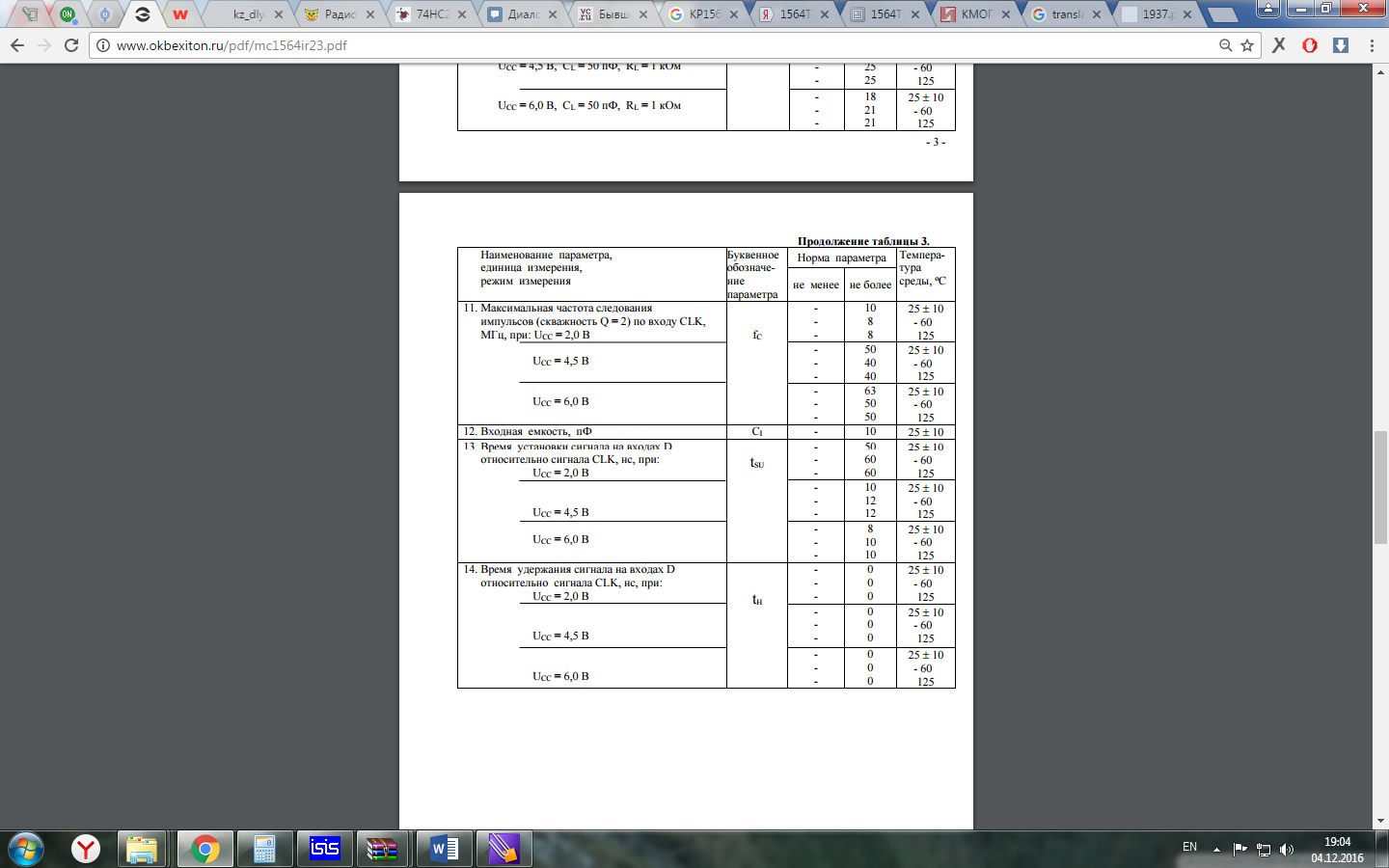

Рисунок 2.14. Электрические параметры микросхемы

Рисунок 2.15. Электрические параметры микросхемы (продолжение)

-

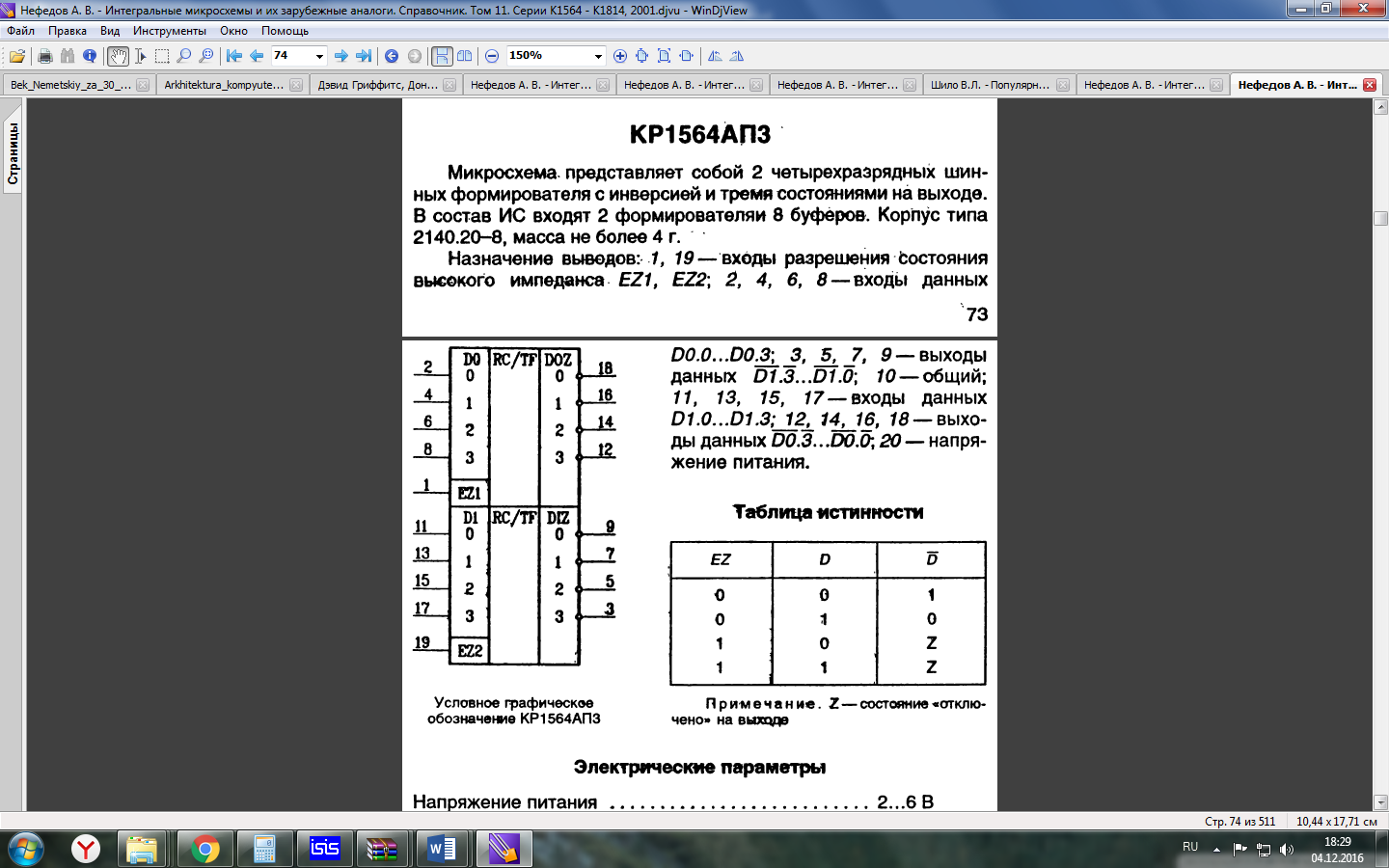

Два четырёхразрядных шинных формирователя с инверсией и тремя состояниями на выходе (КР 1564 АП3).

Рисунок 2.16. Условное графическое обозначение, таблица истинности

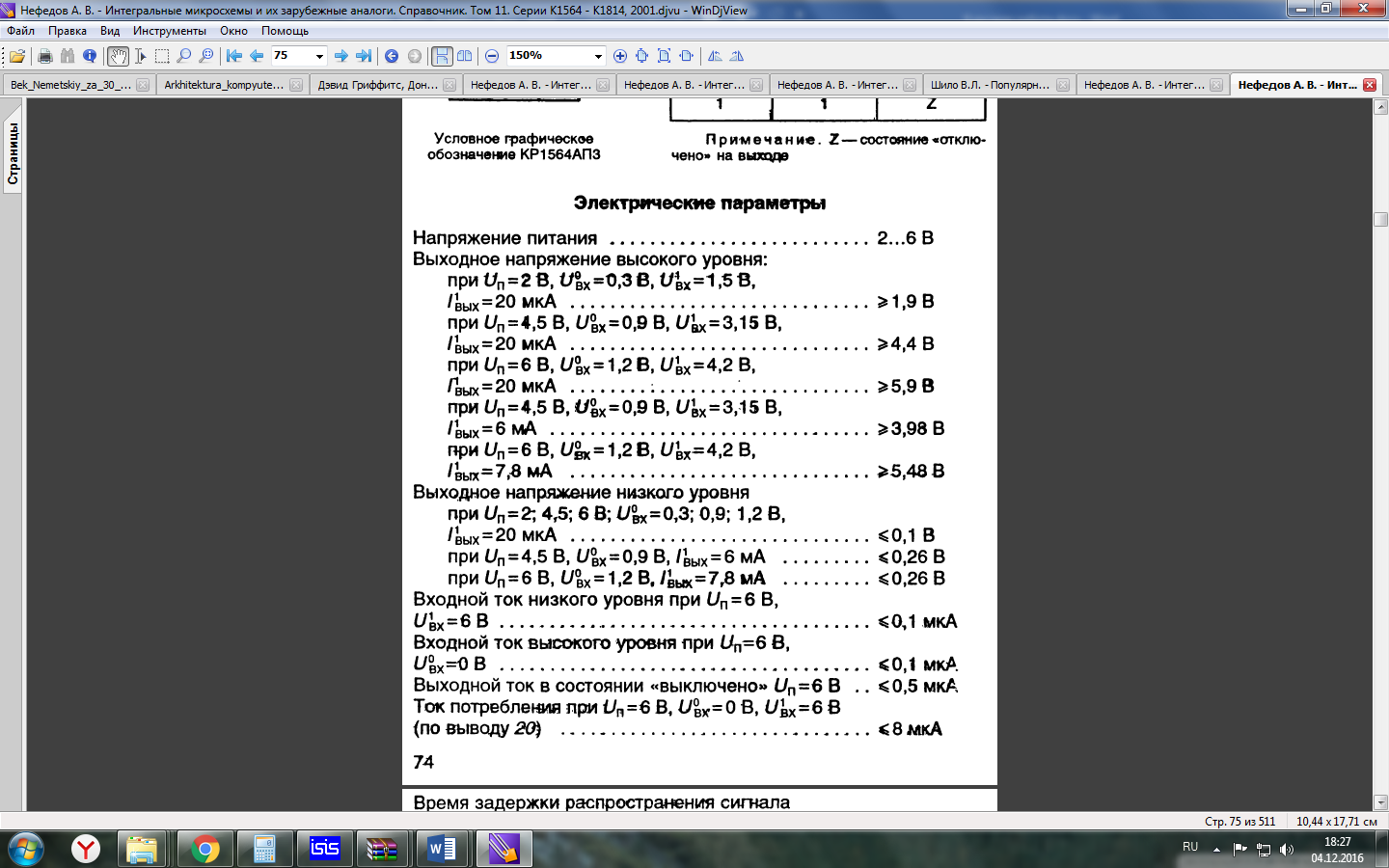

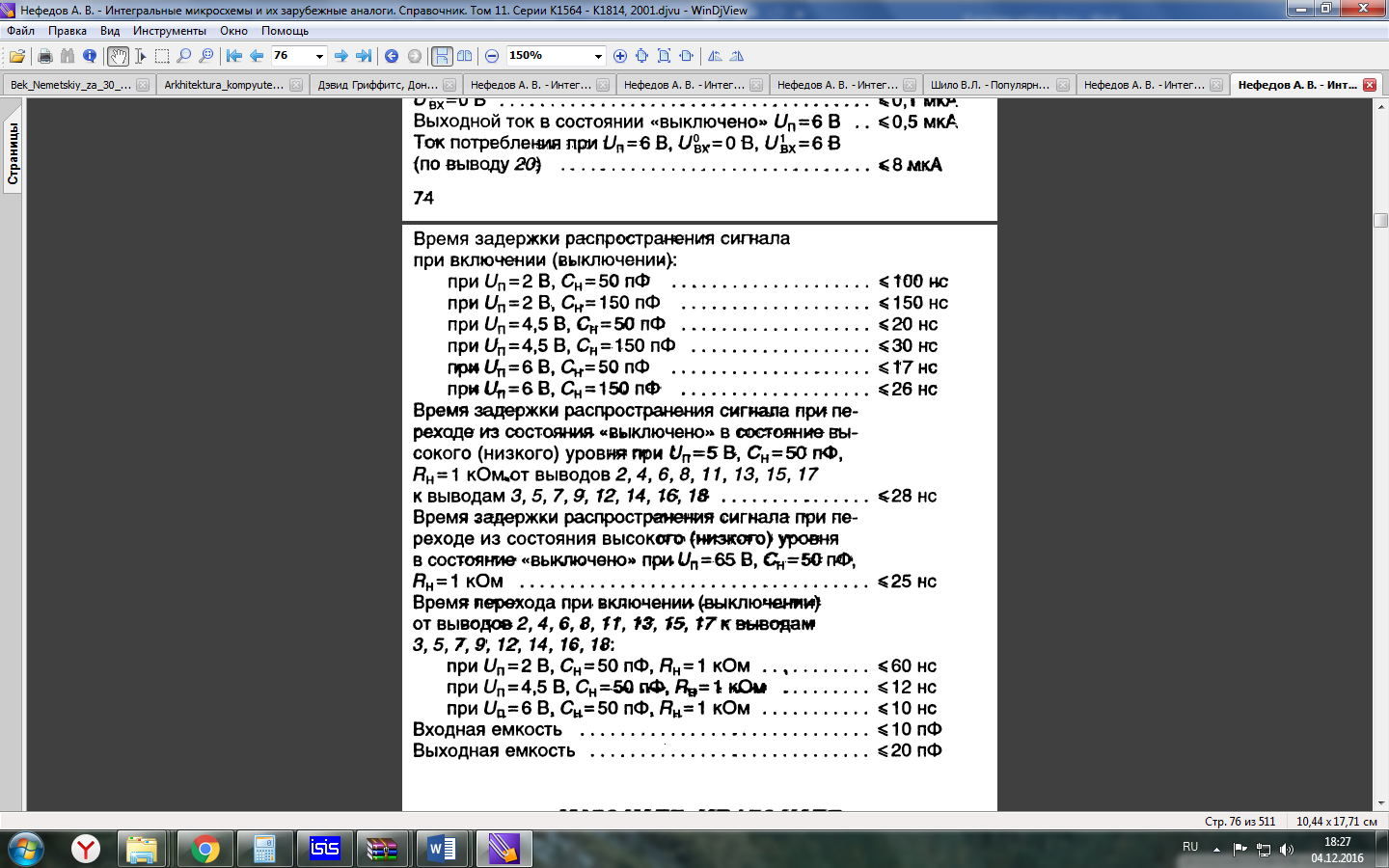

Рисунок 2.17. Электрические параметры микросхемы

-

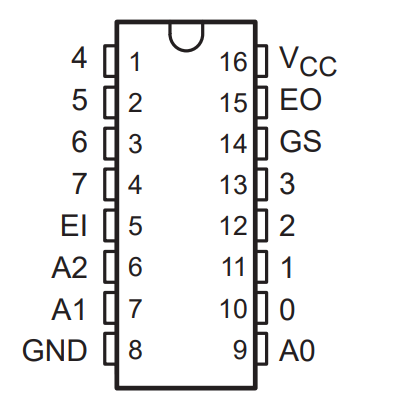

Шифратор приоритетов 8-3 (КР 1564 ИВ1)

Рисунок 2.18. Условное графическое обозначение

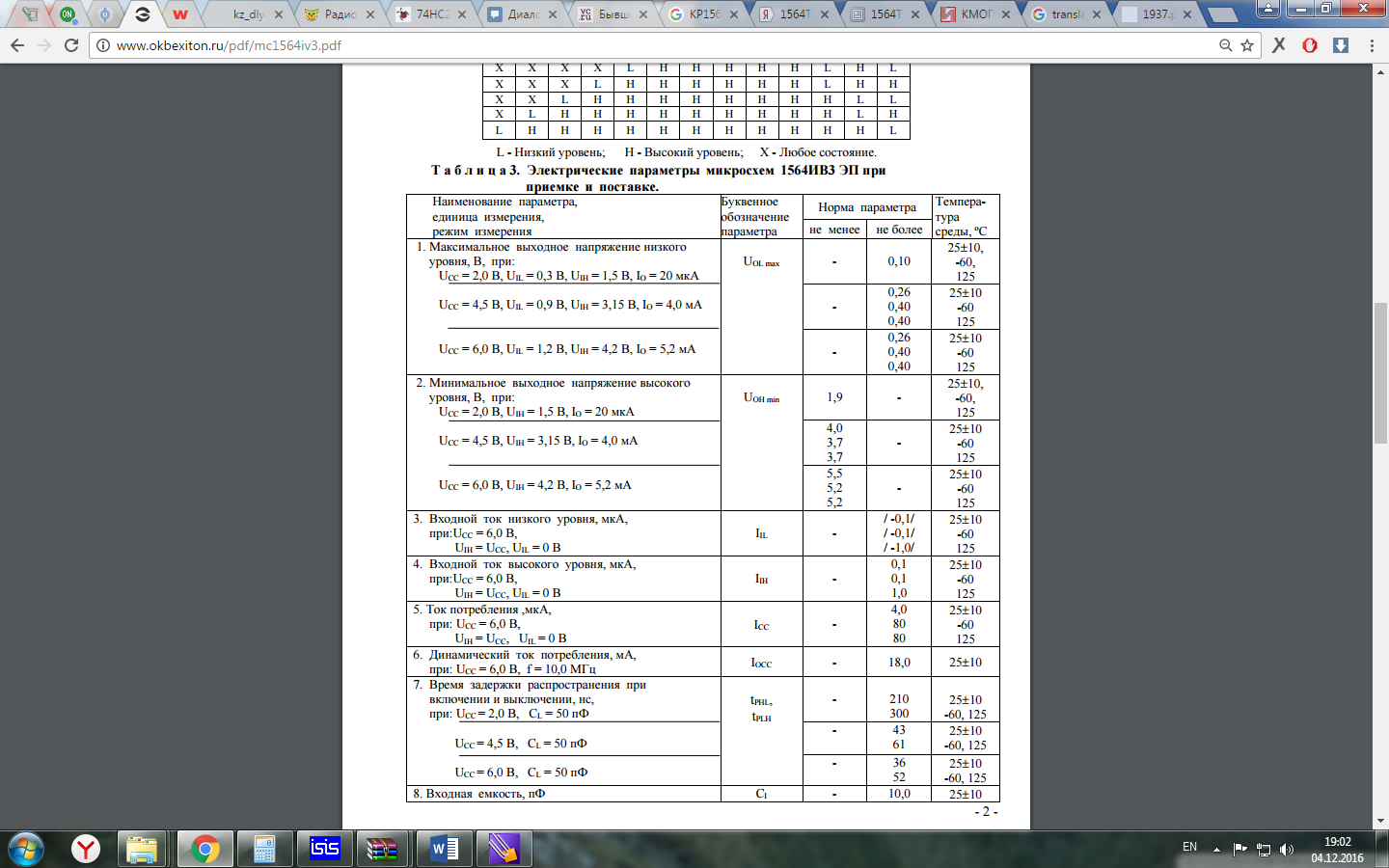

Рисунок 2.19. Электрические параметры микросхемы.

-

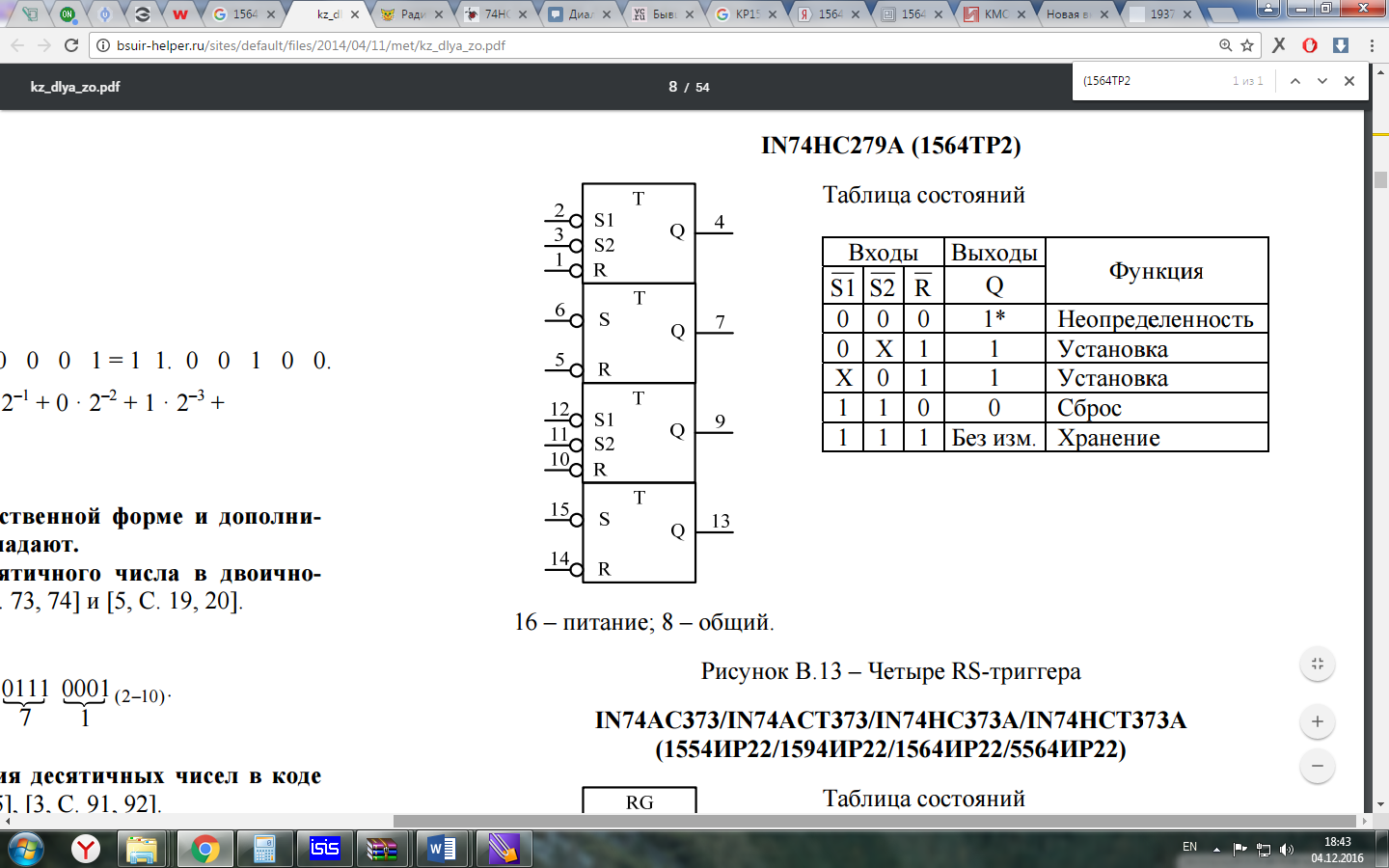

Четыре RS триггера (КР 1564 ТР2)

Диапазон напряжений питания от 2,0 В до 6,0 В.

Диапазон рабочих температур от -40 °С до + 85 °С.

Потребляемый ток питания 2 мкА при 25 °С

Рисунок 2.20. Условное графическое обозначение, таблица состояний.

-

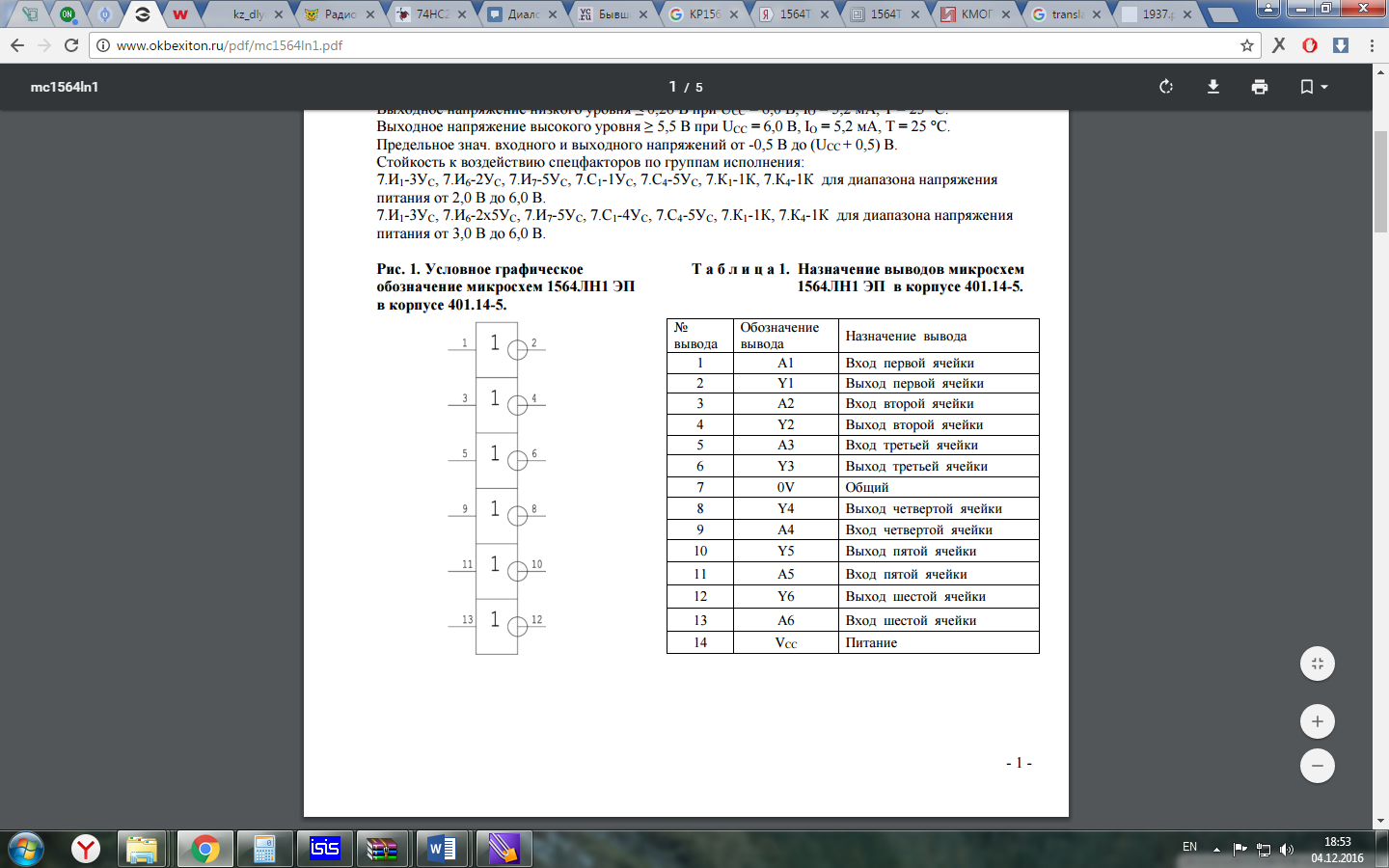

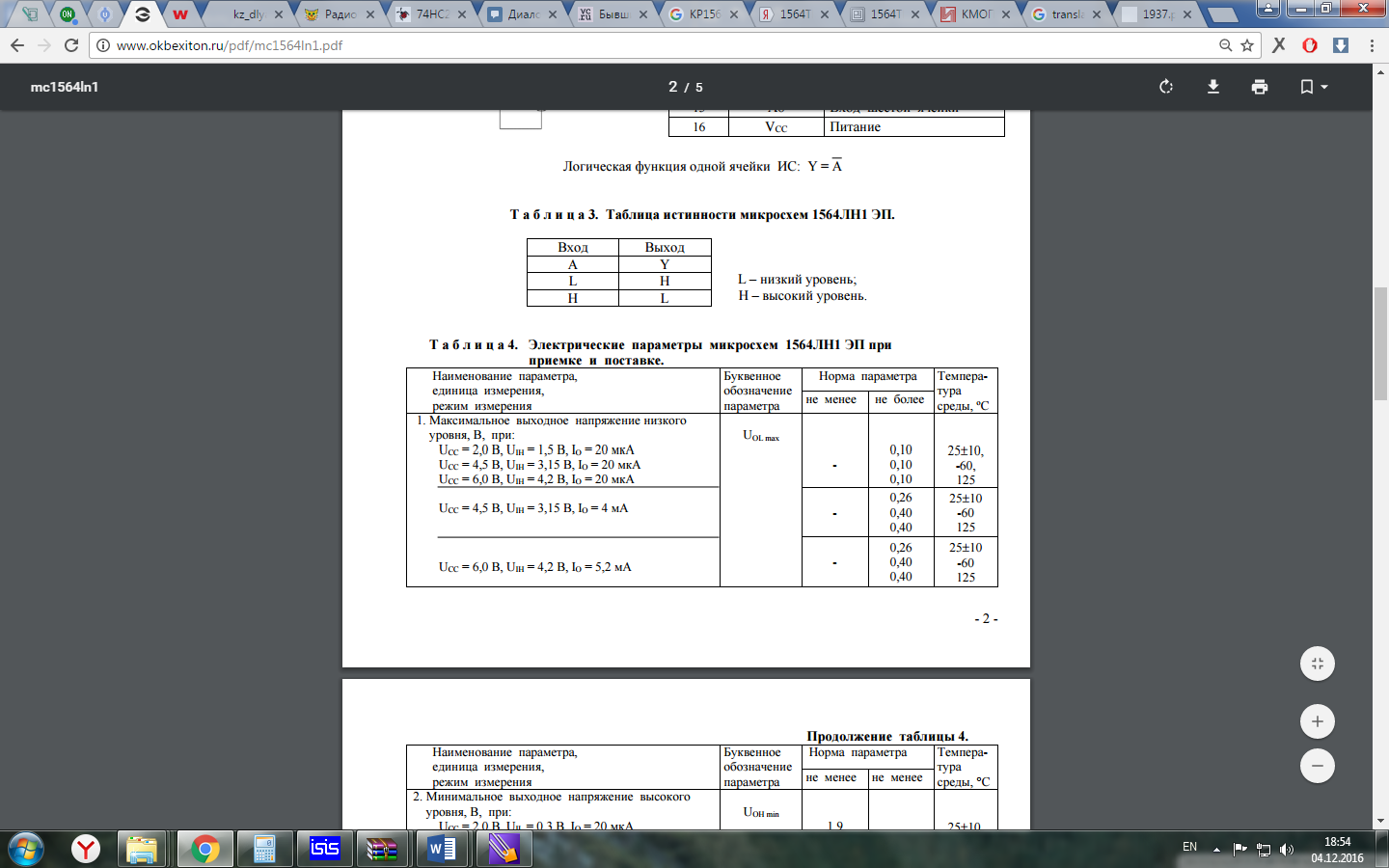

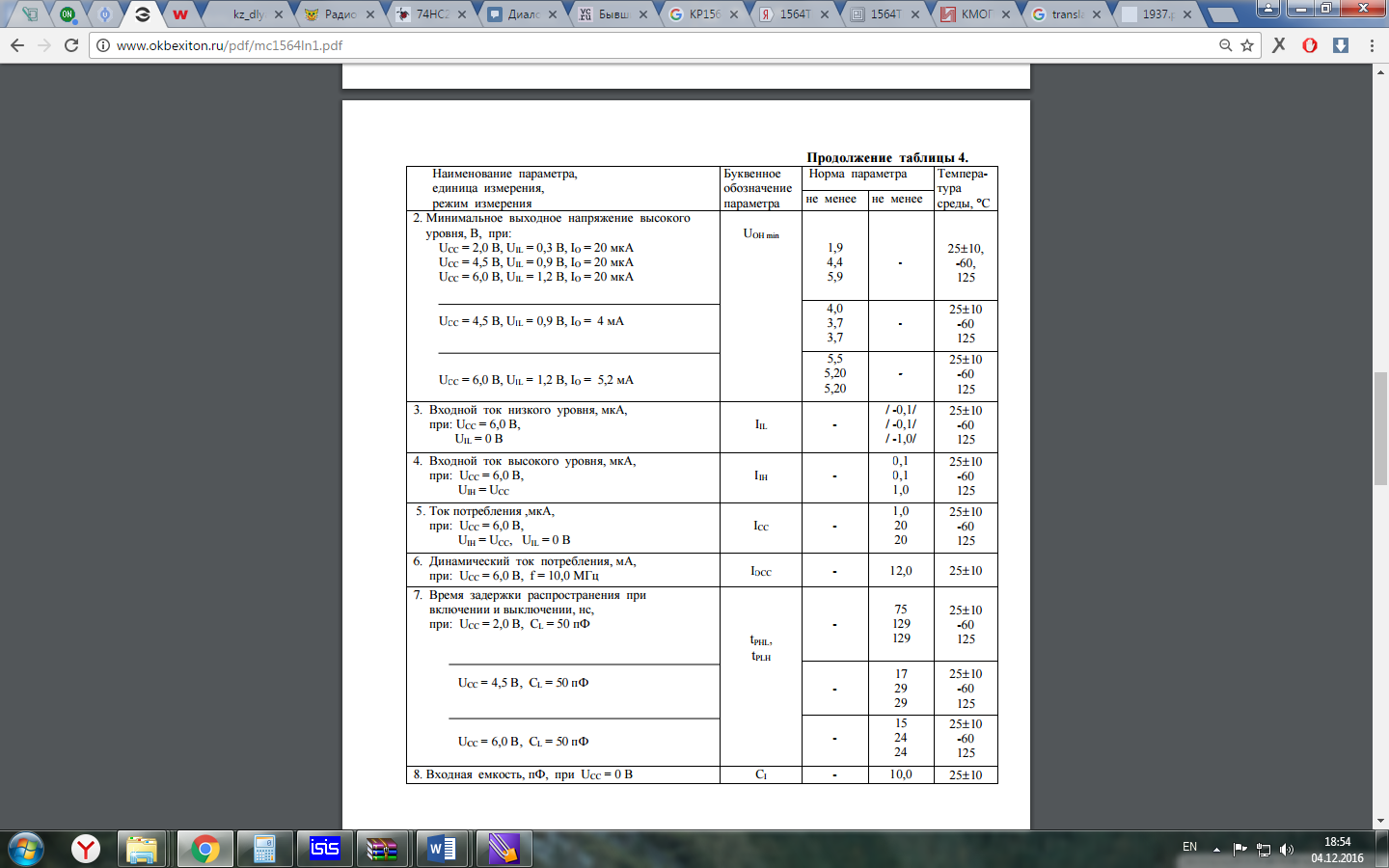

Шесть логических элементов НЕ (1564ЛН1)

Рисунок 2.21. Условное графическое обозначение, назначение выводов.

Рисунок 2.22. Электрические параметры микросхемы.

-

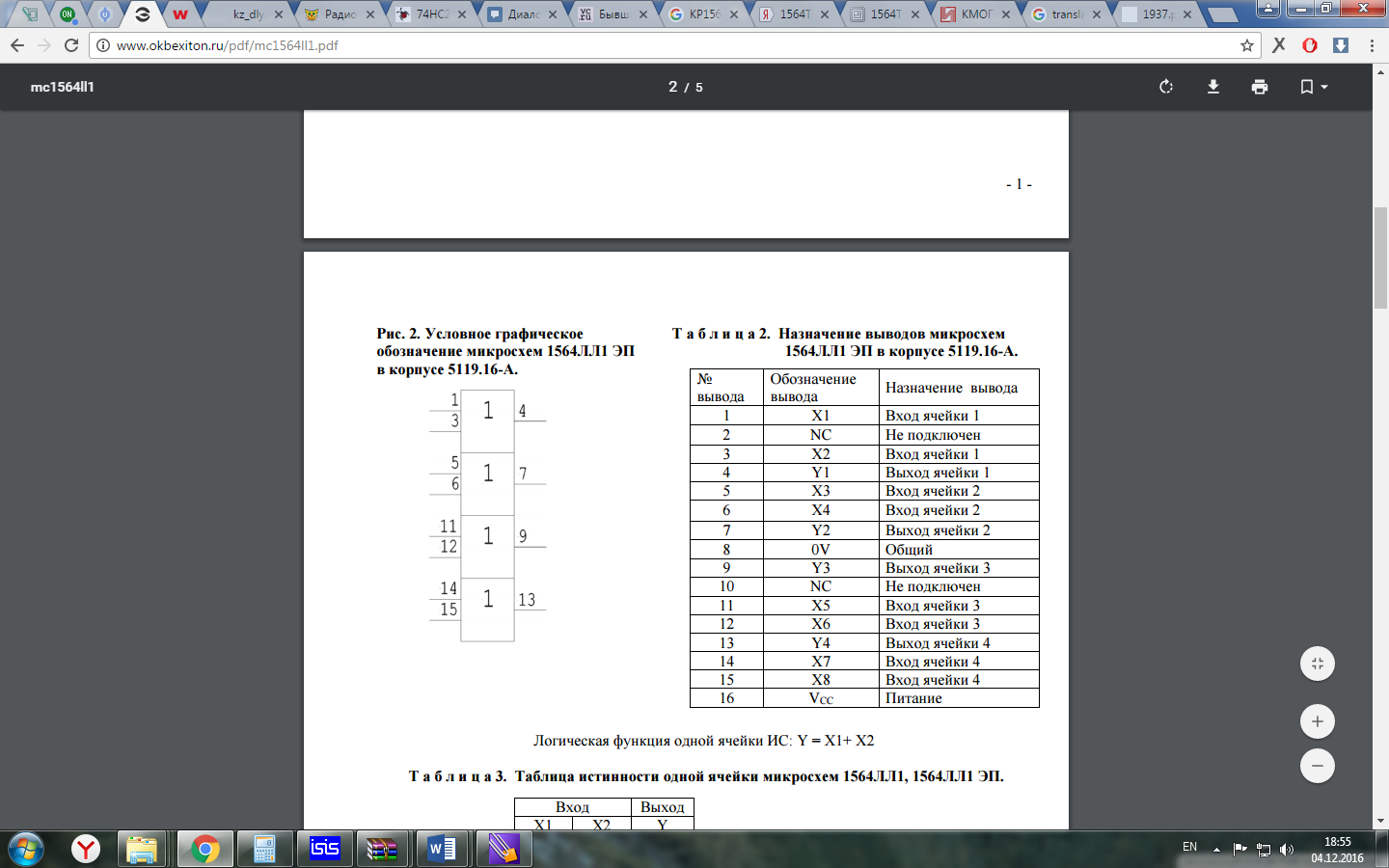

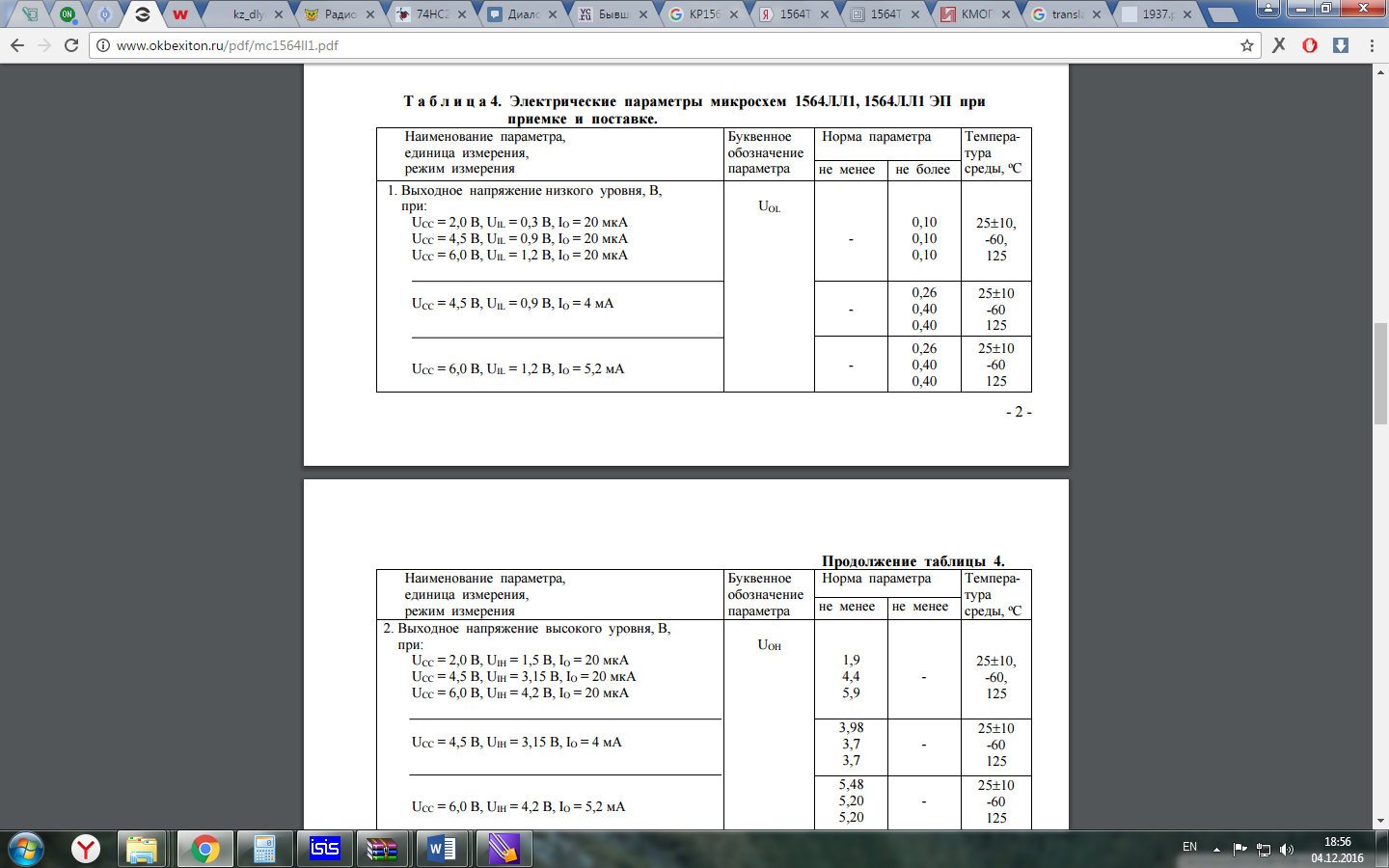

Четыре логических элемента 2ИЛИ (КР1564ЛЛ1)

Рисунок 2.23. Условное графическое обозначение, назначение выводов.

Рисунок 2.24. Электрические параметры микросхемы.

-

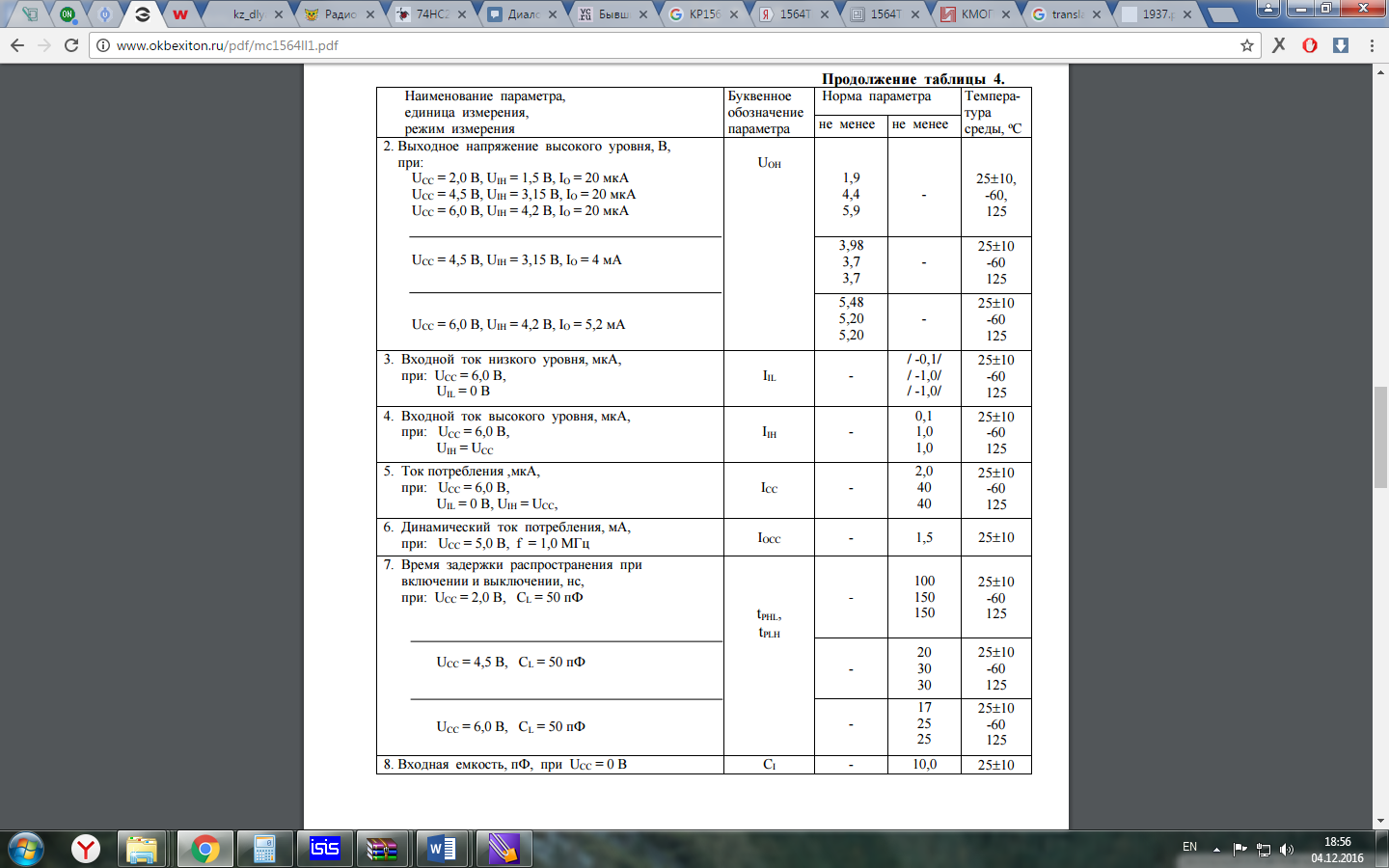

Четыре логических элемента 2И (КР 1564 ЛИ1)

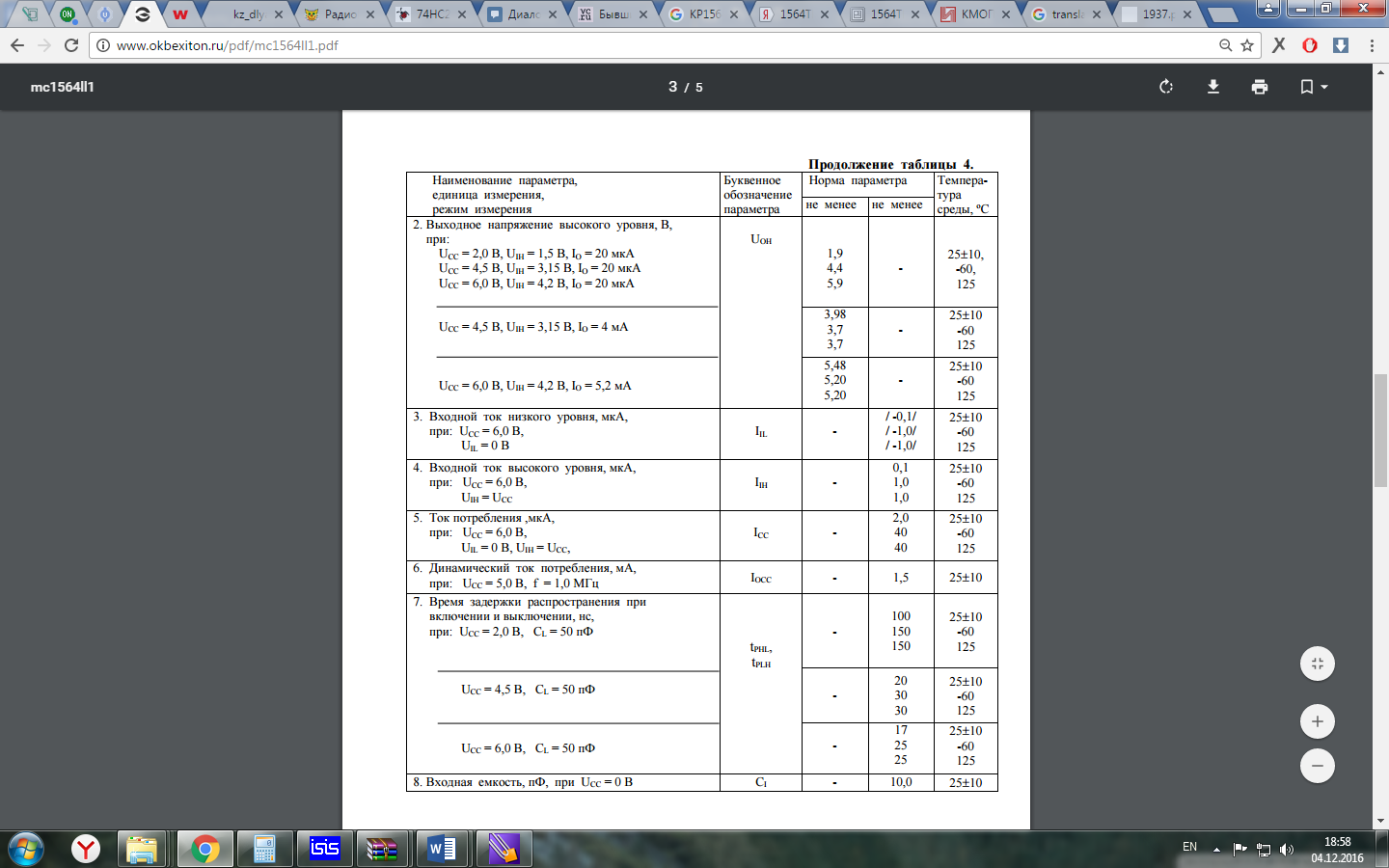

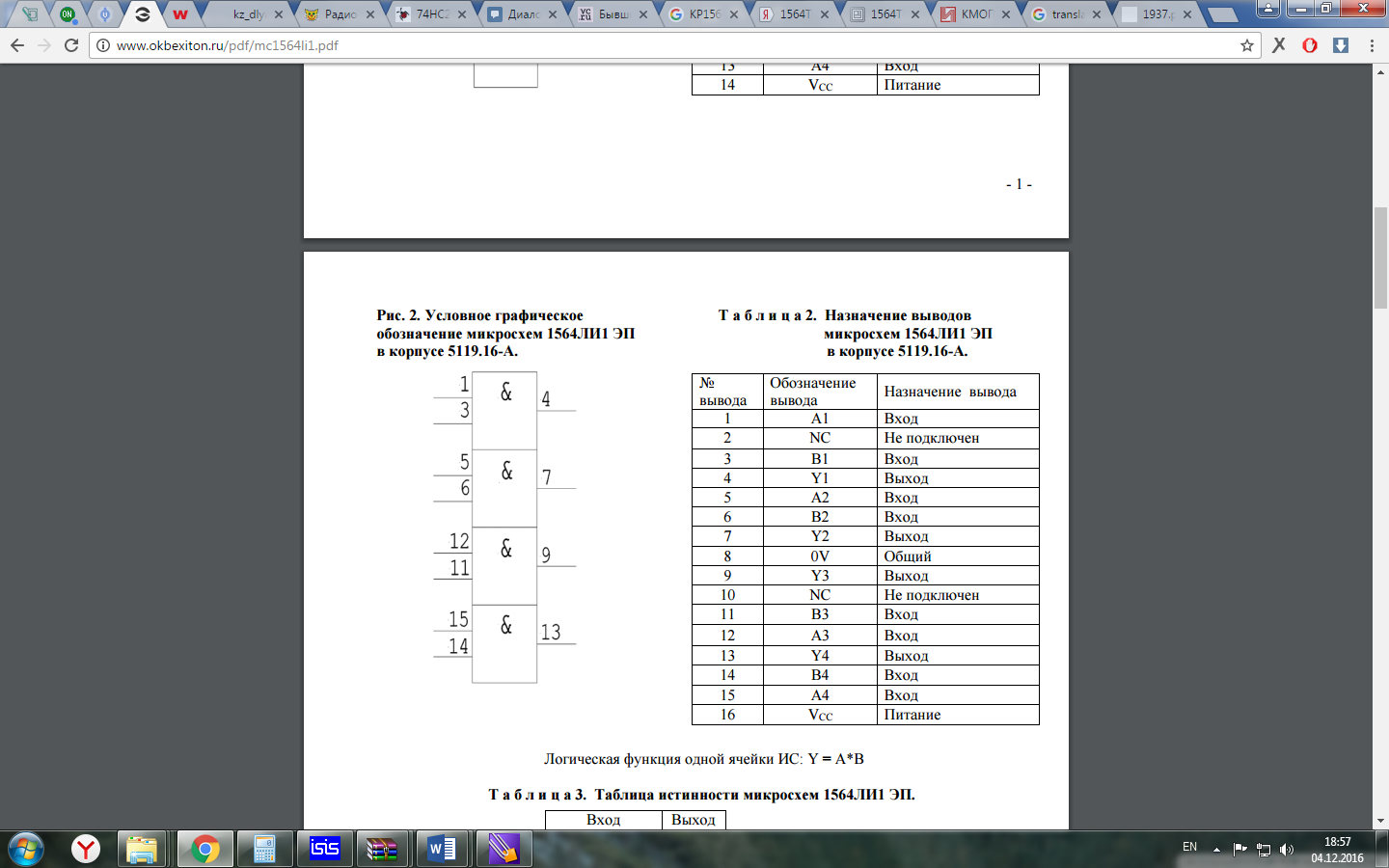

Рисунок 2.25. Условное графическое обозначение, назначение выводов.

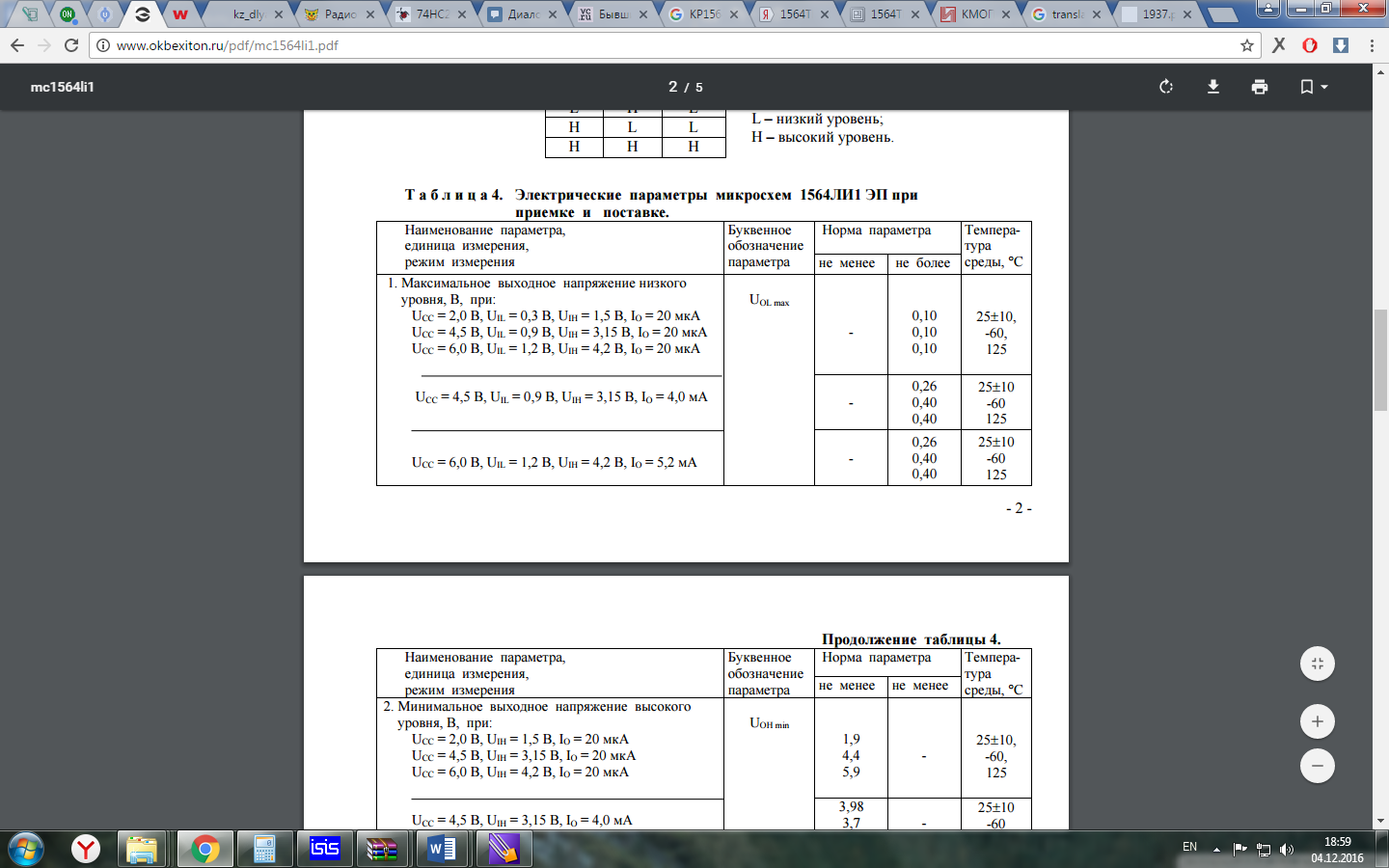

Рисунок 2.26. Электрические параметры микросхемы.

Рисунок 2.27. Электрические параметры микросхемы (продолжение)

-

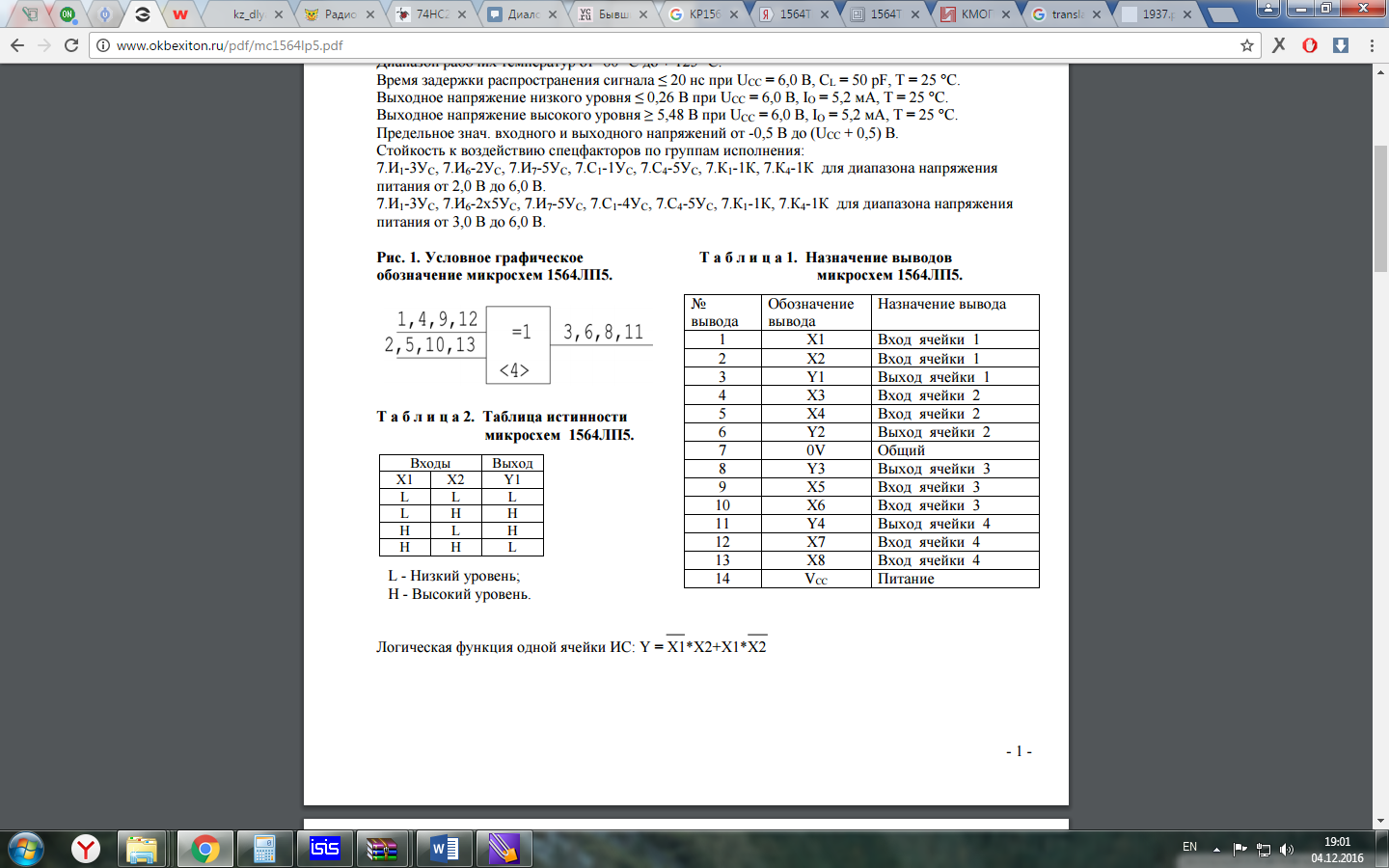

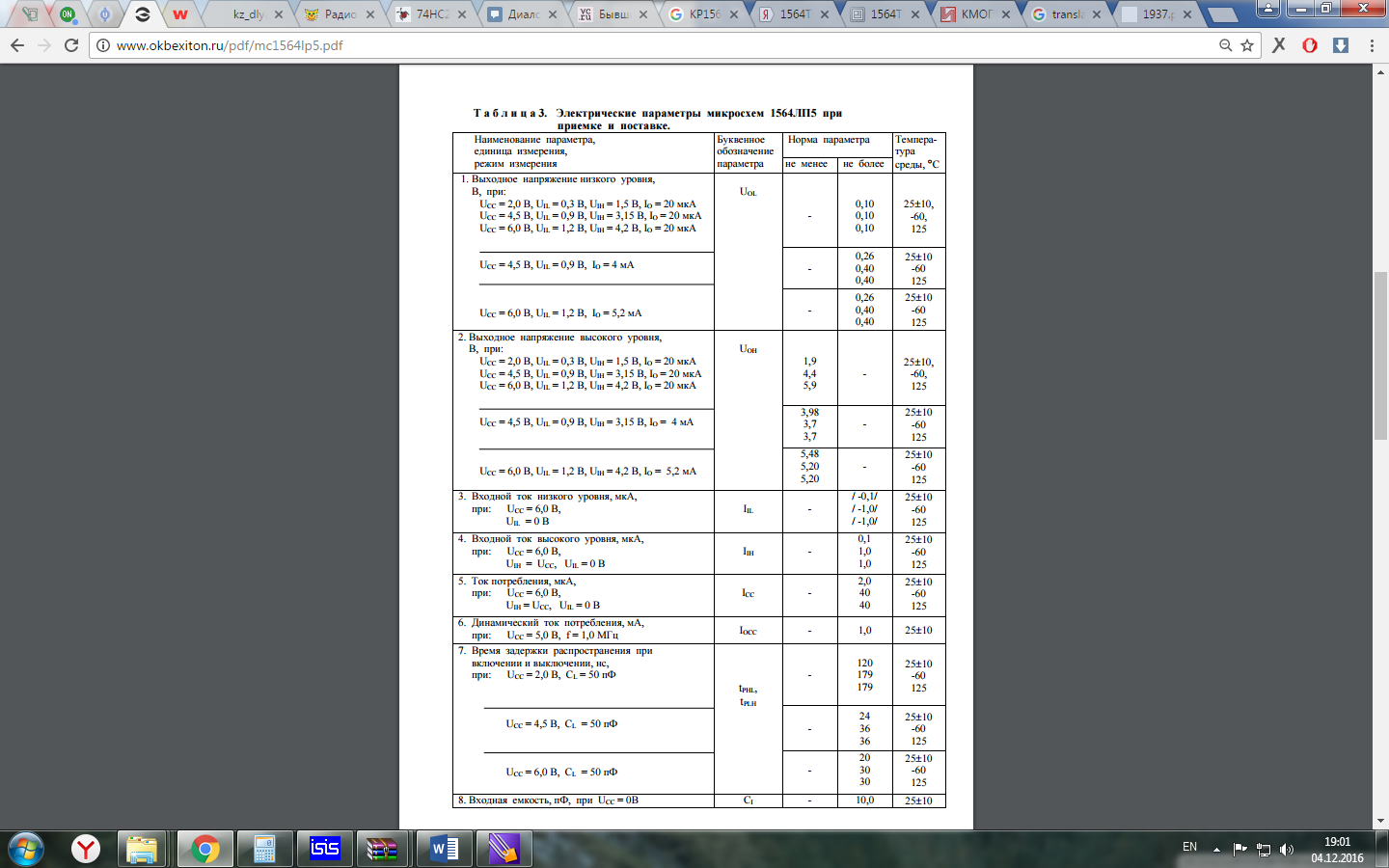

Четыре двухвходовых элемента «исключающее ИЛИ» (КР 1564 ЛП5)

Рисунок 2.28. Условное графическое обозначение, назначение выводов.

Рисунок 2.29. Электрические параметры микросхемы.

-

Расчет мощности потребления и быстродействия микросхем.

-

Восьмиразрядный регистр на D триггерах с общим сбросом

(КР 1564 ИР23)

Pмакс=Iпот*Uпит=8 мкА * 6 В = 48 мкВт

tзад

=18 нс

n = 8 микросхем

Pсумм= Pмакс* n = 48 мкВт * 8 = 384 мкВт

-

Два четырёхразрядных шинных формирователя с инверсией и тремя состояниями на выходе (КР 1564 АП3).

Pмакс=Iпот*Uпит=8 мкА * 6 В = 48 мкВт

tзад =10 нс

n = 16 микросхем

Pсумм= Pмакс* n = 48 мкВт * 16 = 768 мкВт

-

Шифратор приоритетов 8-3 (КР 1564 ИВ1)

Pмакс=Iпот*Uпит=4 мкА * 6 В = 24 мкВт

tзад =36 нс

n = 2 микросхем

Pсумм= Pмакс* n = 24 мкВт * 2 = 48 мкВт

-

4 RS триггера (КР 1564 ТР2)

Pмакс=Iпот*Uпит=2 мкА * 6 В = 12 мкВт

tзад =7 нс

n = 1 микросхем

Pсумм= Pмакс* n = 12 мкВт * 1 = 12 мкВт

-

Шесть логических элементов НЕ (1564ЛН1)

Pмакс=Iпот*Uпит=2 мкА * 6 В = 12 мкВт

tзад =7 нс

n = 14 микросхем

Pсумм= Pмакс* n = 12 мкВт * 14 = 168 мкВт

-

4 элемента 2ИЛИ (КР1564ЛЛ1)

Pмакс=Iпот*Uпит=2 мкА * 6 В = 12 мкВт

tзад =17 нс

n = 20 микросхем

Pсумм= Pмакс* n = 12 мкВт * 20 = 240 мкВт

-

4 логических элемента 2И (КР 1564 ЛИ1)

Pмакс=Iпот*Uпит=2 мкА * 6 В = 12 мкВт

tзад =17 нс

n = 17 микросхем

Pсумм= Pмакс* n = 12 мкВт * 17 = 204 мкВт

-

Четыре двухвходовых элемента «Исключающее ИЛИ»

(КР 1564 ЛП5)

Pмакс=Iпот*Uпит=2 мкА * 6 В = 12 мкА

tзад =20 нс

n = 16 микросхем

Pсумм= Pмакс* n = 12 мкВт * 16 = 192 мкВт

Мощность всей микросхемы равна:

P = 384 + 768 + 48 + 12 + 168 + 240 + 204 + 192= 2016 мкВт = 2 мВт

Из приведённых выше расчетов видно, что суммарная мощность потребления всех микросхем вычислительного устройства равна 2 мВт, что удовлетворяет заданному ограничению в 100 мВт.

-

Расчет задержки прохождения сигнала