ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.12.2023

Просмотров: 24

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

ВВЕДЕНИЕ

Первой предпосылкой к появлению программируемых логических интегральных схем стало появление первых постоянных запоминающих устройств в 70-х годах прошлого столетия.После этого в истории микроэлектроники осуществляется планомерное развитие устройств с программируемой логикой как вычислительных устройств, применимых для решения обширного круга задач цифровой обработки информации. Наиболее яркий след в развитии цифровых вычислительных устройств оказало появление первых микропроцессоров. Данное событие открыло двери широкому применению цифровых технологий обработки информации. Однако микропроцессоры не всегда актуальны при решении задач в цифровой схемотехнике: принцип работы микропроцессора основан на микропрограмме и представляет собой последовательность шагов конечной длительности, в то время как для многих задач требуются устройства, у которых задержка при выполнении логических функций будет минимальной. Наиболее удобным способом решения данных задач и являются логические программируемые интегральные схемы (ПЛИС). Программируемая логическая интегральная схема — электронный компонент, предназначенный для создания цифровых интегральных схем. Принципиальное отличие ПЛИС от обычных цифровых микросхем, заключается в том, что логика работы ПЛИС, задаётся посредством программирования, а не определяется при изготовлении. На данный момент лидерами в сфере программируемых логических интегральных схем являются три фирмы: Xilinx, Inc, компания Actel Corporation и фирма Altera Corporation. На долю этих трех гигантов приходится львиная доля рынка ПЛИС.

1 ТЕМАТИЧЕСКИЙ ОБЗОР

Программируемые логические интегральные схемы

При программировании на ПЛИС можно задавать разную структуру цифрового устройства. Цифровое устройство можно задать в виде программы на специальных языках описания аппаратуры или в качестве принципиальной электрической схемы. В качестве языков описания аппаратуры используются например: Verilog, VHDL, AHDL. Программируемые логические интегральные схемы — являются одним из наиболее перспективных и динамично развивающихся сегментов цифровой схемотехники. ПЛИС является кристаллом, с расположенными на нем простыми логическими элементами, не соединенными между собой. Соединение данных логических элементов, то есть формирование электрической схемы, происходит благодаря электронным ключам, которые расположены в этом же кристалле. Управление электронными ключами происходит посредством специальной памяти. Принцип работы специальной памяти заключается в помещении кода конфигурации цифровой схемы в её ячейки, и записав данные коды в память ПЛИС можно собрать цифровое устройство различной степени сложности и с необходимыми параметрами, а также с разным количеством элементов на кристалле. Одним из отличий ПЛИС от микропроцессоров заключается в том, что алгоритмы цифровой обработки можно организовать на аппаратном уровне. В данном случае быстродействие цифровой обработки увеличиться. Разберем классификацию ПЛИС по структуре. Основным критерием данной классификации является наличие логических матриц, а также их вид и способ коммутации. Согласно данной классификации выделяют следующие классы ПЛИС: – Программируемые логические матрицы — самый ранний тип ПЛИС, появившийся в 70-е года прошлого века, в котором и матрицы «И», и матрицы «ИЛИ» являются программируемыми. – Программируемая матричная логика — это тип ПЛИС, имеющих программируемую матрицу «И» и фиксированную матрицу «ИЛИ». – Программируемая макрологика — это ПЛИС, в которых есть одна программируемая матрица «И-НЕ» или «ИЛИ-НЕ», при этом способные формировать сложные логические функции благодаря инверсным обратным связям. – Программируемые коммутируемые матричные блоки — ПЛИС, которые содержат, объединенные коммутационной матрицей, матричные логические блоки, обычно в количестве 4–8 штук. – Программируемые вентильные матрицы — состоят из логических блоков, включающие в свой состав несколько более простых логических элементов, на базе таблицы перекодировки, программируемого мультиплексора, D-триггера, цепи управления. А также коммутирующих путей — программируемых матриц соединений. Программируемые логические интегральные схемы являются более совершенными

нежели обычные цифровые микросхемы и микропроцессоры, и поэтому обладает целым рядом преимуществ, такими как: минимальное время разработки схемы, так как требуется всего лишь занести в память ПЛИС конфигурационный код, возможность быстрого изменения в цифровой схеме, отсутствие потребности в разработке и изготовлении сложных печатных плат, а также в сложном технологическом производстве и оборудовании. ПЛИС конфигурируется с помощью обычного персонального компьютера. В качестве недостатка ПЛИС можно указать лишь их более высокую стоимость по сравнению с аналогами, такими как микропроцессоры и обычные цифровые микросхемы. Основной сферой применения ПЛИС является создание цифровых устройств с различными возможностями и степенями сложности, например: устройств, требующих высокую скорость передачи данных, а также сложных устройств, требующих большое количество портов ввода-вывода. Устройств для выполнения цифровой обработки сигналов. Различных видов цифровой видеоаппаратуры и аудиоаппаратуры. Устройств, предназначенных для системы защиты информации, и для проектирования интегральных схем специального назначения. Коммутирующих устройств, задачей которых является обеспечения взаимодействия между системами с различной логикой и напряжением питания. Устройств, нашедших применение при обработке радиолокационной информации и моделировании квантовых вычислений. Также при помощи ПЛИС могут реализовываться нейрочипы. В данное время программируемые логические интегральные схемы охватывают множество областей, в которых находят широкое применение. Одной из таких областей является цифровая обработка сигналов. ПЛИС помогают разработчикам создавать цифровую электронную аппаратуру, принцип работы которых основан на реализации алгоритмов цифровой обработки сигналов.

2 РАЗРАБОТКА СТРУКТУРЫ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

Проектирование микропроцессорной системы включает в себя четыре этапа.

Первый этап. Системный – производится описание функций, выполняемых будущей микропроцессорной системой, составляется спецификация на систему (определяется структура, номенклатура и особенности построения программных и микропрограммных средств).

Второй этап. Производится разработка структуры микропроцессорной системы, выбор микропроцессорных наборов на базе которых будет реализовываться микропроцессорная система, определяются связи между программным и аппаратным обеспечением.

Третий этап. Разработка и изготовление опытного образца, разработка соответствующего программного обеспечения, разработка системы ввода/вывода. Разработка программ состоит из: разработки алгоритмов вычислений, написания текста исходных программ, трансляции исходных программ в исходный код, автономной отладки программного обеспечения.

Четвертый этап. Комплексная отладка программного и аппаратного обеспечения микропроцессорной системы. Процесс отладки представляет собой процесс обнаружения ошибок и определения источника их появления по результатам тестирования. Для проведения отладки проектируемая микропроцессорная система должна обладать свойствами управляемости, наблюдаемости и предсказуемости.

2.1 Разработка общей структуры вычислительного устройства

При построении вычислительного устройства, как правило, используется модульный принцип организации, при этом в минимальный состав должны входить:

-

операционный автомат; -

устройство управления; -

память; -

устройство ввода/вывода информации.

Для организации связи между модулями вычислительного устройства используется магистральный способ, который обеспечивает минимальный набор связей между модулями и, как следствие, высокое быстродействие системы.

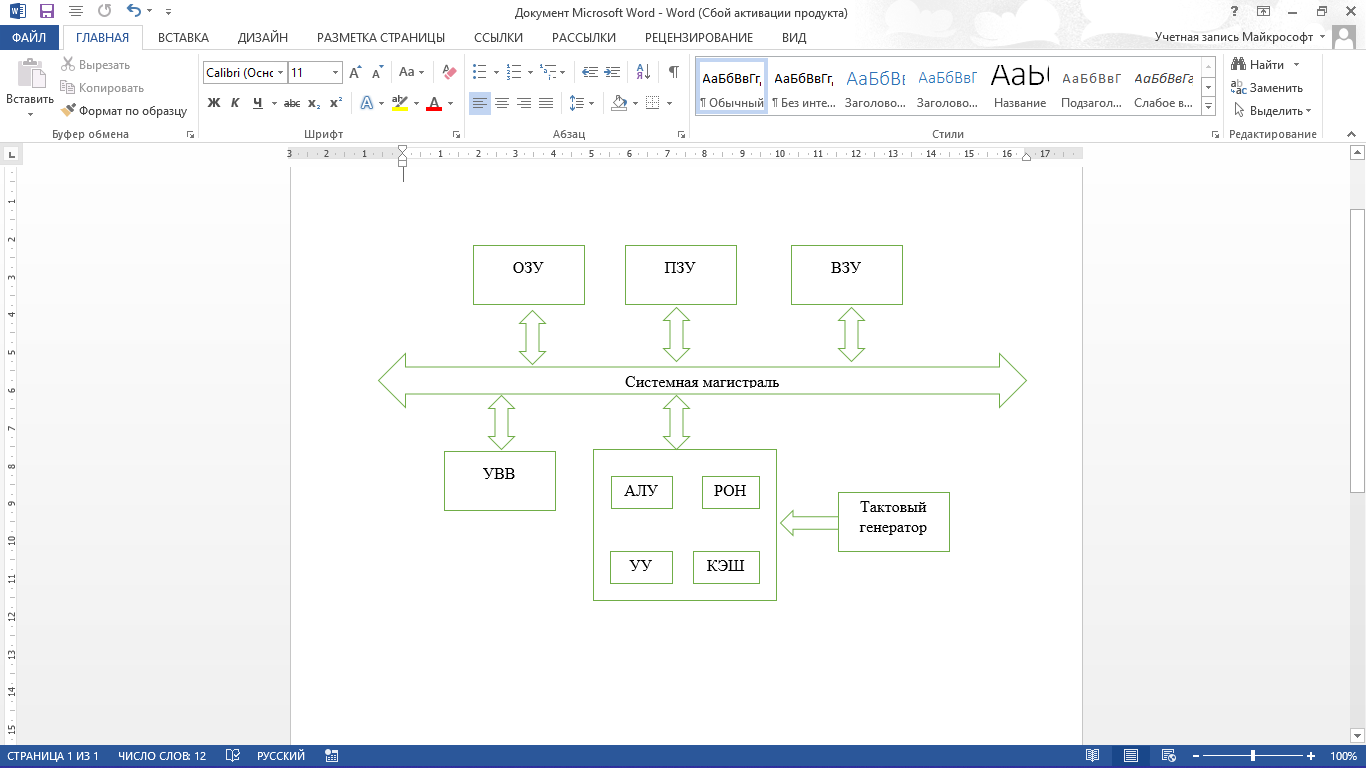

На рисунке 1 представим обобщенную структурную схему вычислительного устройства между узлами которой связи осуществляются по системной магистрали.

Рисунок 1 – Обобщенная структурная схема ЭВМ с шиной организации

На данной схеме использованы следующие сокращения:

-

ОЗУ – оперативное запоминающее устройство; -

ПЗУ – постоянное запоминающее устройство; -

ВЗУ – внешнее запоминающее устройство; -

УВВ – устройство ввода-вывода; -

АЛУ – арифметико-логическое устройство; -

РОН – регистры общего назначения; -

УУ – управляющее устройство; -

КЭШ – промежуточный буфер с быстрым доступом к содержащейся в нем информации.

Системная магистраль микропроцессорной системы представляет собой совокупность стандартного набора сигналов, проводов по которым они передаются и правил обмена между устройствами подключенных к магистрали.

На физическом уровне системная магистраль состоит из трех шин: шины данных, шины адреса и шины управления. Шина данных (ШД) используется для передачи информационных кодов между всеми устройствами микропроцессорной системы. Число проводников, составляющих шину данных называют ее разрядностью.2 Шина адреса (ША) используется для передачи адресов ячеек памяти и портов ввода-вывода с которыми процессор обменивается информацией в данный момент. Шина управления (ШУ) состоит из отдельных проводов по каждому из которых передаются отдельные управляющие сигналы.

Производительность цифрового устройства определяется разрядностью шины данных, а объем адресного пространства – разрядностью шины адреса.

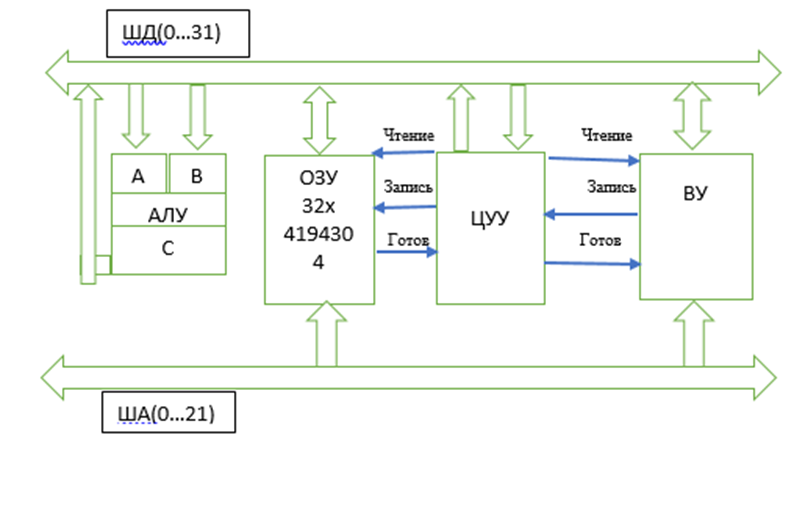

Рассчитаем разрядность шины адреса используя формулу:

| | m=  | (1) |

где N – емкость ОЗУ в битах.

Вычислим:

N = 128 Кбайт = 1048576 бит,

m =

= 20 бит

= 20 битБазовым элементом любого вычислительного устройства является программно-управляемый модуль. Структурную схему которого представим на рисунке 2.

Рисунок 2 – Структурная схема программно-управляемого модуля

2.2 Разработка арифметико-логического устройства

Все основные операции по преобразованию данных производятся в операционных блоках, составляющих арифметико-логическое устройство (АЛУ). В зависимости от выполняемых функций АЛУ можно разделить на две части:

-

устройство управления, которое задает последовательность микрокоманд; -

операционное устройство, в котором реализуется заданная последовательность микрокоманд.

АЛУ представляет собой функционально и логически законченный блок процессора, который под управлением устройства управления и синхроимпульса (УУ и С) служит для выполнения арифметических и логических преобразований над данными, называемых операндами.

В любом АЛУ предусмотрена возможность выполнения четырех основных арифметических операций, нескольких логических операций, а также сдвигов.

В составе АЛУ можно выделить четыре основные группы узлов.

Первая группа - узлы хранения:

-

регистры, обеспечивающие хранение операндов, промежуточных и окончательных данных; -

триггеры, позволяющие хранить различные признаки результатов.

Вторая группа – узлы передач:

-

мультиплексоры, обеспечивающие выполнение передач по выбранному маршруту; -

шины соединяющие отдельные блоки АЛУ; -

блоки вентилей, обеспечивающие передачу информации в определенный момент времени.

Третья группа – узлы преобразования:

-

сумматоры, выполняющие различные микрооперации; -

схемы выполнения логических операций; -

схемы сдвига; -

счетчики, используемые для вспомогательных преобразований.

Четвертая группа – узлы управления:

-

дешифраторы управляющих сигналов; -

блок управления АЛУ; -

схемы формирований логических условий.

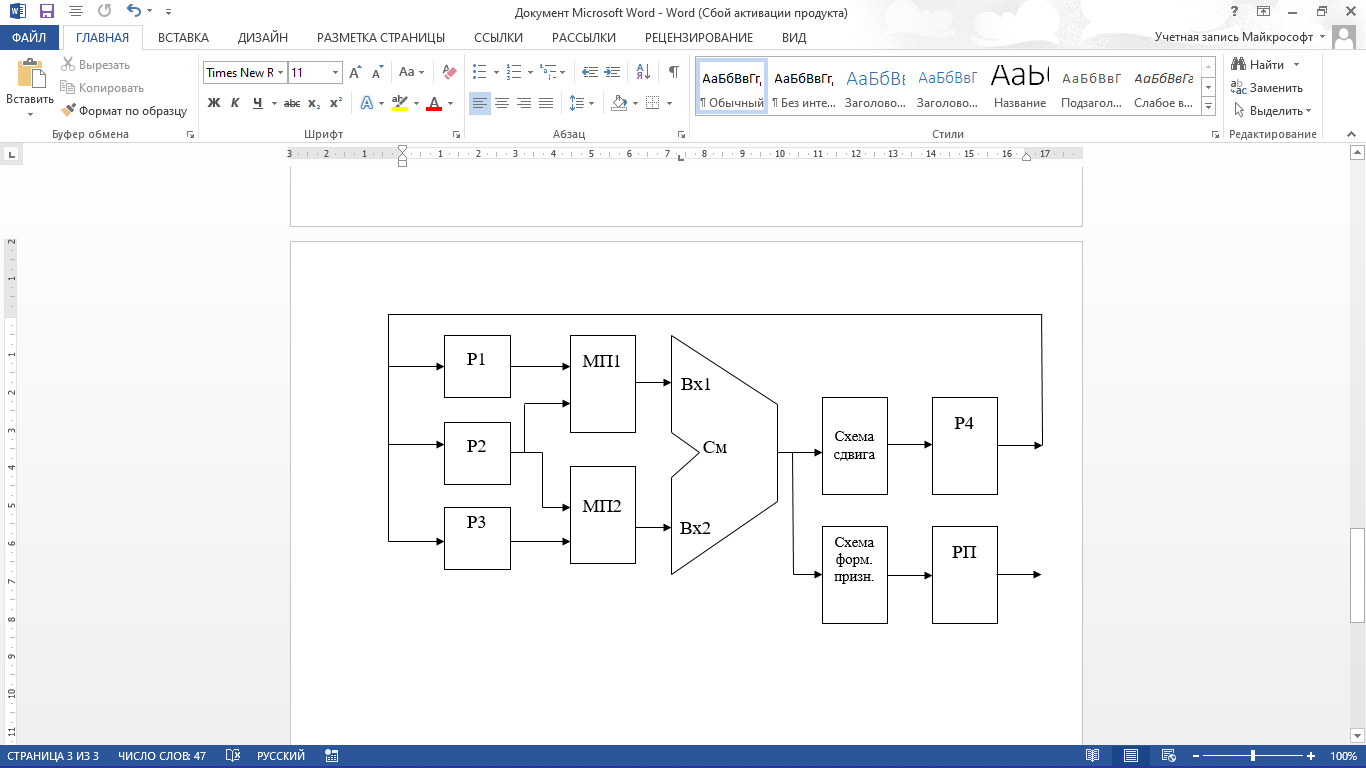

Структуру простейшего типового АЛУ представим на рисунке 3.

Рисунок 3 – Схема простейшего АЛУ

На данной схеме используются следующие обозначения:

-

Р1, Р2, Р3, Р4 – регистры; -

МП1, МП2 – мультиплексоры; -

См – сумматор; -

РП – регистр признака.

Обрабатываемая в АЛУ информация представляет собой численные или логические величины. Это проявляется в используемых формах представления данных, системах счисления, разрядности, применяемых кодах. На рисунке 4 представим схему классификации АЛУ.

Рисунок 4 – Классификация АЛУ

2.3 Разработка алгоритмов арифметических и логических операций

2.3.1 Алгоритм операции сложения/вычитания

При сложении двух чисел, представленных в прямом и обратном коде, соблюдаются правила двоичной арифметики. Единица переноса, возникающая в старшем знаковом разряде суммы, отбрасывается, если число представляется в формате с фиксированной запятой. При вычитании возникает необходимость занимать единицу из старшего разряда. Операции сложения/вычитания выполняются за один такт операционного автомата.

Рассмотрим операцию сложения/вычитания на примере чисел

А = 6 (0110) и В =2 (0010)

Для формата RR: в регистр АХ пометим число 0111, в регистр ВХ – 0010, а результат вычисления поместив в регистр СХ.

Для формата SS: в регистр АХ пометим число 0111, в регистр ВХ – 0010, а результат вычисления поместив в регистр СХ.

Произведем вычисления суммы и разности:

С = А + В = 0110 + 0010 = 1000

С = А - В = 0111 - 0010 =0100

Реализуем инструкции сложения и вычитания на ассемблере, используя регистры общего назначения.

Операция сложения для формата RR:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010

ADD AX, BX; складываем значение регистров

mov CX, AX; в регистр СХ помещаем содержимое регистра АХ

Операция вычитания для формата RR:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010

SUB AX, BX; вычитание значение регистров

mov CX,AX; в регистр СХ помещаем содержимое регистра АХ

Операция сложения для формата SS:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010