ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.12.2023

Просмотров: 25

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

NКОП – число операций.

Вычислим

Rкоп =int(log229)= 4 бит

Число разрядов, отводимых под поле способа адресации вычислим по формуле:

где NCA – число способов адресации.

Вычислим

Rca = int(log24)= 2 бит

В адресной части команды содержится информация об исходных данных, их месте нахождения и месте сохранения результата операции. Обычно место нахождения каждого из операндов и результата задается в команде путем указания адреса соответствующей ячейки основной памяти или номером регистра процессора. Принципы использования информации из адресной части определяет система адресации, которая задает число адресов в команде. Разрядность поля адреса вычислим по формуле:

Вычислим:

RA =int(log2 20)=5 бит

Для указанных в задании форматов команд рассчитаем общую длину команды, учитывая, что число адресов в команде равно:

Для формата RR l=2:

Rk =2*5+5+1=16

Для формата SS l=4:

Rk =4*5+5+1=26

Для рассчитанных форматов составим таблицу команд.

Таблица 1 – Таблица команд.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | ||||

| КОП | СА | S1 | S2 | B3 | D4 | ||||||||||||||||||||||||

| КОП | СА | R1 | S2 | | | | | | | | | | | ||||||||||||||||

2.4.2 Расчет производительности устройства

Оценка производительности вычислительных систем может осуществляться по различным методикам. Одной из таких методик является определение производительности по весу арифметических действий, выполняемых процессором:

, (6)

, (6)где ai – вес арифметического действия;

ti – среднее время выполнения арифметического действия.

На примере универсального микропроцессорного комплекта, оценим производительность устройства согласно исходным данным приведенным в таблице 2.

Таблица 2 – Веса и время выполнения арифметических действий

| Область применения микроконтроллера (МК) и МП | Передача данных между МП и памятью | Групповые пересылки регистров | Однооперандные команды | Двухоперандные команды | Команды передачи управления | Различные команды | |||

| Сложение | Вычитание | Деление | Умножение | ||||||

| ai | 74 | 12 | 40 | 15 | 14 | 13 | 19 | 40 | 20 |

| ti | 0,379 | 0,420 | 0,372 | 0,356 | 0,356 | 0,374 | 0,368 | 0,503 | 0,4 |

Р=74+12+40+15+14+13+19+40+20/74*0,379+12*0,420+40*0,372+15*0,356+14*0,356+13*0,374+19*0,368+40*0,503+20*0,4=247/98,264=2,51

2.4.3 Разработка операционного автомата

Любая операция в вычислительном устройстве рассматривается, как сложное действие, которое разделяется на последовательность элементарных операций над словами информации. Для хранения слов информации, выполнения набора микроопераций и вычисления значений логических условий используется операционный автомат. Его структура определяется общей длиной команды и форматом выполняемых операций.

Управление работой операционного автомата осуществляется с помощью управляющего автомата, который генерирует последовательность управляющих сигналов, т.е. задает порядок действий в операционном автомате.

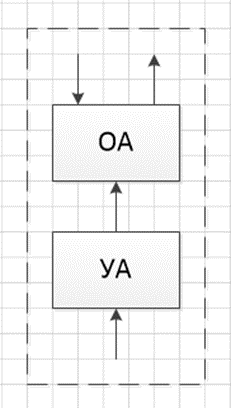

Операционный и управляющий автоматы составляют блок операционного устройства служащий для обработки цифровой информации. На рисунке 14 показано операционное устройство.

Рисунок 14 – Операционное устройство

Основными узлами операционного устройства являются: регистр команд (RK), счетчик команд (PC), регистр адреса (RA), регистр стека (SP), управляющий автомат (YA).

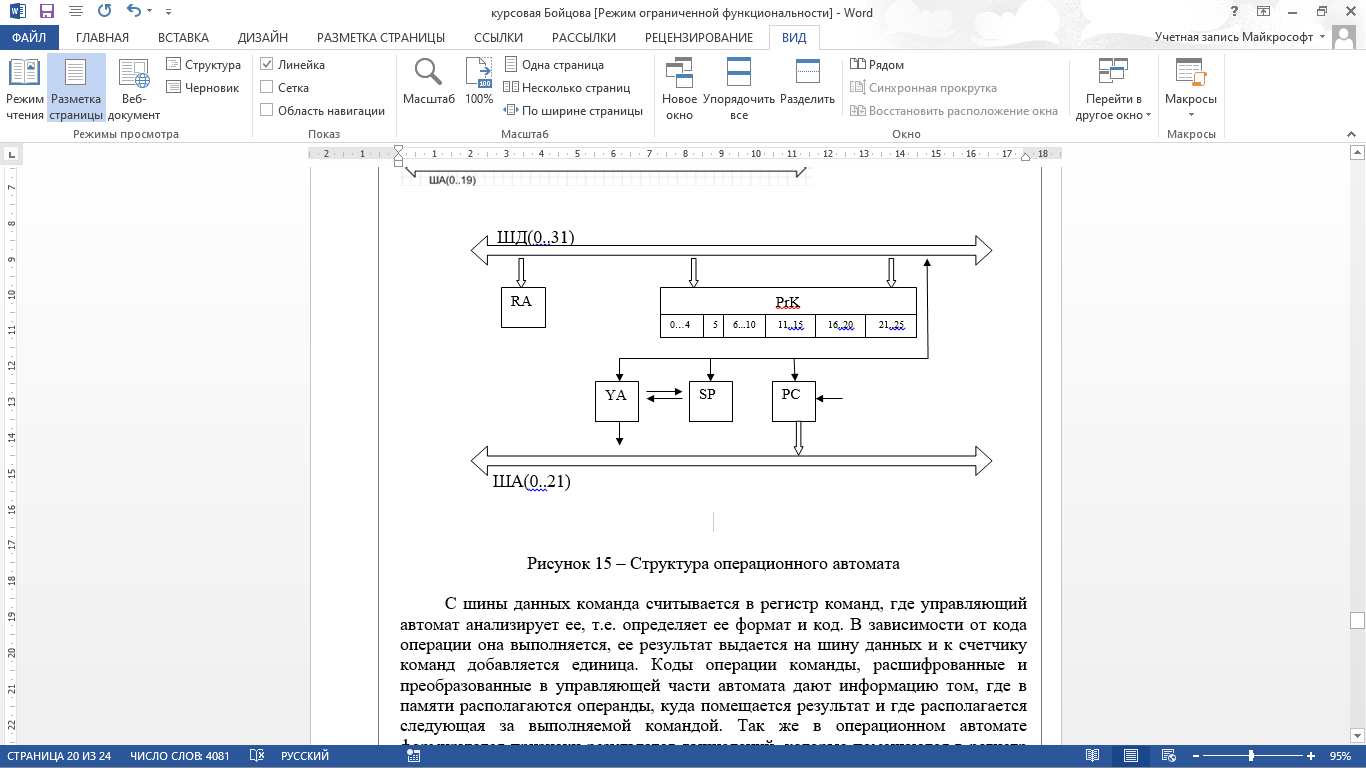

Рисунок 15 – Структура операционного автомата

С шины данных команда считывается в регистр команд, где управляющий автомат анализирует ее, т.е. определяет ее формат и код. В зависимости от кода операции она выполняется, ее результат выдается на шину данных и к счетчику команд добавляется единица. Коды операции команды, расшифрованные и преобразованные в управляющей части автомата дают информацию том, где в памяти располагаются операнды, куда помещается результат и где располагается следующая за выполняемой командой. Так же в операционном автомате формируются признаки результатов вычислений, которые помещаются в регистр стека.

2.5 Структура запоминающего устройства

Запоминающее устройство вспоминает запись, хранение и считывание произвольной двоичной информации. Оно является основным устройством памяти цифровых систем, в котором хранятся программы, определяющие процесс текущей обработки информации. Связь с запоминающим устройством осуществляется по системной магистрали. По шине данных передается информация, записываемая в память и считываемая из нее. По шине адреса передается адрес, участвующий в обмене элемента памяти.

Согласно заданию:

-

емкость 512 – 4194304 бит; -

разрядность ЗУ – 24 бит; -

разрядность ША – 20 бит; -

разрядность ШД – 16 бит.

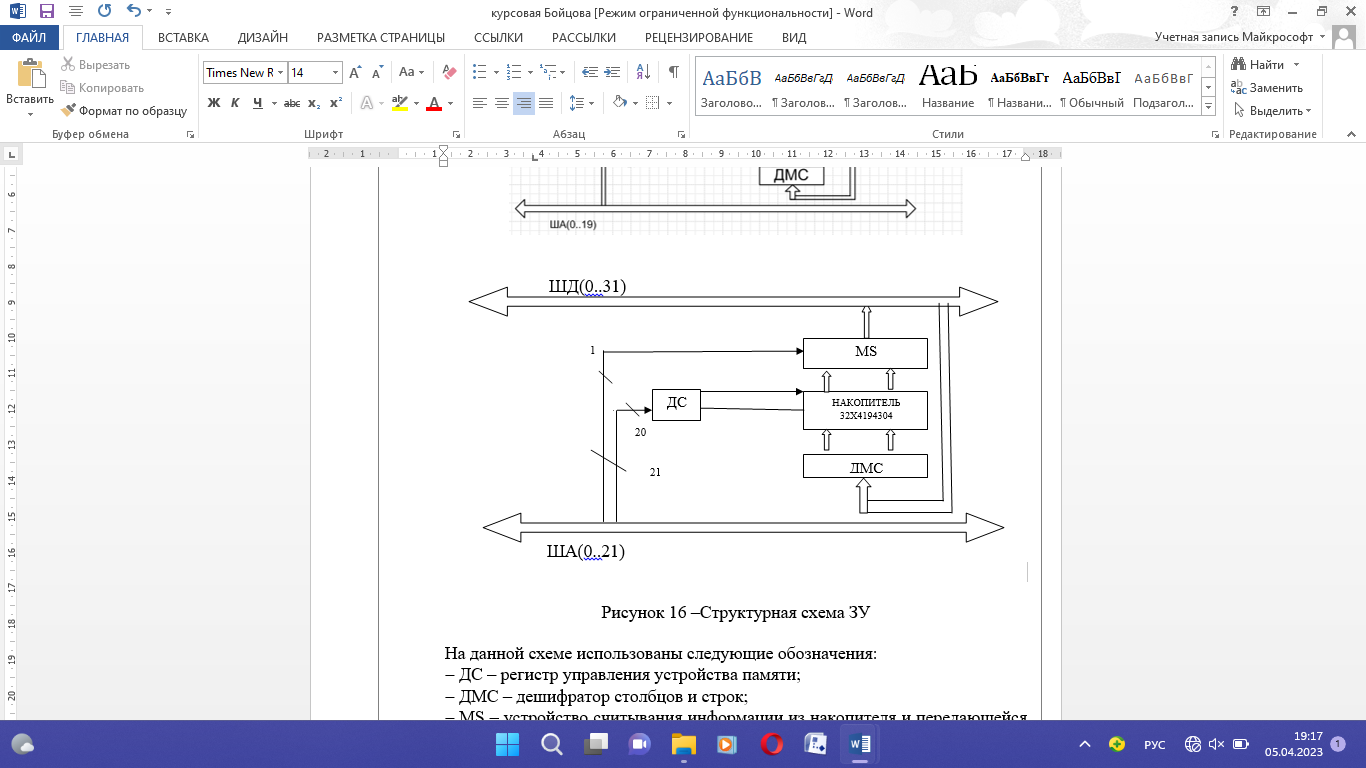

На рисунке 16 представим структурную схему ЗУ.

Рисунок 16 –Структурная схема ЗУ

На данной схеме использованы следующие обозначения:

-

ДС – регистр управления устройства памяти; -

ДМС – дешифратор столбцов и строк; -

MS – устройство считывания информации из накопителя и передающейся на ШД.

ЗАКЛЮЧЕНИЕ

Благодаря основным признакам проектирования МПС: модульности, микропрограммируемости и магистральности можно разработать вычислительное устройство по отдельным модулям, а затем объединить их в единое целое. Основным узлом таких устройств является центральная вычислительная машина в структуре, которой можно выделить АЛУ, управляющие и операционные автоматы и шины, соединяющие эти узлы между собой.

Внедрение микропроцессорных комплектов открыло возможность построения многофункциональных приборов с гибким программным обеспечением, сделало такие приборы более экономичными и облегчило задачи ввода/вывода данных на стандартную интерфейсную шину и управление самим интерфейсом.

В данном курсовом проекте были рассмотрены принципы построения основных узлов вычислительного устройства, выполняющего основные арифметические и логические операции, а также команды пересылки данных.

При изучении основных принципов разработки вычислительного устройства с указанным набором команд была описана структура устройства, операционный автомат АЛУ, работы управляющего автомата, выполнен алгоритм реализации основных операций, рассмотрена структура запоминающего устройства.