ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.12.2023

Просмотров: 26

Скачиваний: 1

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

ADD AX, BX; складываем значение регистров

mov CX, AX; в регистр СХ помещаем содержимое регистра АХ

Операция вычитания для формата SS:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010

SUB AX, BX; вычитание значение регистров

mov CX, AX; в регистр СХ помещаем содержимое регистра АХ

2.3.2 Алгоритм операции произведения

Операция произведения выполняется за несколько тактов операционного автомата. Умножение вычисления как сумма частичных произведений, каждая из которых получается последовательными сдвигами и умножением множимого на соответствующий разряд множителя.

Рассмотрим выполнение алгоритма умножения двоичных чисел в прямом коде, начиная с младших разрядов со сдвигом частичного произведения.

А = 0111, Апр = 0,0110

В = 0010, Впр = 0,0010

Sign[A] = 0; Sign[B] = 0

C1 = Апр * B1 * 2-1 = 0,0111*0*2-1 = 0,0110*0*0,1 = 0

C2 = Апр * B2 * 2-2 = 0,0111*1*2-2 = 0,0110*1*0,01 =110

C3 = Апр * B3 * 2-3 = 0,0111*0*2-3 = 0,0110*0*0,001 = 0

C4 = Апр * B4 * 2-4 = 0,0111*0*2-4 = 0,0110*0*0,0001 = 0

С = С1+С2+С3+С4 = 0+0,000110+0+0 = 0,00001110

Проверка

0,0110

0,0010

00000

00111

0,00001100

Операция умножения в ассемблере выполняется с помощью инструкции MUL, которая может работать только с регистрами общего назначения или памятью и не может работать непосредственно с числами. Данная инструкция имеет одинаковый синтаксис для всех форматов:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010

MUL AX, BX; перемножаем содержимое регистров АХ и ВХ, результат помещаем в АХ.

Если в результате вычисления получается число более 8 бит, то для хранения результата вычисления будет использоваться пара регистров DX и AX.

2.3.3 Алгоритм операции деления

Операция деления выполняется за несколько тактов операционного автомата. Для операндов с фиксированной запятой она осуществляется путем последовательного вычисления кода делителя из кода делимого и определения знака остатка.

Реализовать операцию деления можно двумя способами:

˗ деление с неподвижным делимым и сдвигаемым вправо делителем;

˗ деление с неподвижным делителем и сдвигаемым влево делимым.

Произведем операцию деления с неподвижным делителем и сдвигаемым влево делимым без восстановления остатка. Для реализации данной операции для чисел А и В запишем прямой код, а для делителя В запишем еще дополнительный код.

А=0110 Апр=0,0110

В=0010 Впр=0,0010 Вдоп.=1,1101+0,0001=1,1110

Частное

-

0,0110

1,1101 1

0,0011

-

0,1010

1,1101 11

1,1101 110,0011

-

0,0110

1,1101 111

0,0011

-

0,0110

1,1101 1110

0,0011

-

0,0110

0,0010 11100

1,1000

За четыре сдвига мы получаем целую часть частного 10111 и положительный остаток 0,0001.

Деление ассемблере выполняется с помощью инструкции DIV, которая реализуется за несколько тактов операционного автомата. Данная команда не работает непосредственно с числами или сегментными регистрами, а только с регистрами общего назначения или областью памяти. Данная инструкция имеет одинаковый синтаксис для всех форматов:

mov AX, 0110; помещаем в регистр АХ значение 0110

mov BX, 0010; помещаем в регистр BX значение 0010

DIV AX, BX; выполняется деление чисел А/В, результат операции заносится в регистр АХ.

Если при делении получается остаток, то его записывают в регистр АН.

2.3.4 Алгоритм логических операций

Логические операции под соответствующими операндами выполняются комбинационными схемами АЛУ. Основными логическими операциями являются: инверсия, конъюнкция, дизъюнкция и эквивалентность. Данные операции перечислены в сложном логическом выражении, для соблюдения которого используют скобки. Логические операции выполняются за 1 такт операционного автомата.

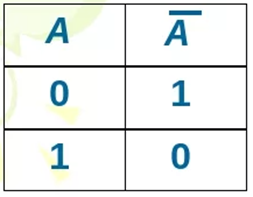

Инверсия – битовая операция, при выполнении которой результат отрицания всегда противоположен значению аргумента.

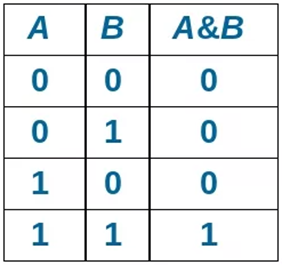

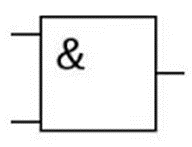

Конъюнкция – это функция двух, трех и более переменных и выполняется по правилу: результат равен 1, если все операнды равны 1, во всех остальных случаях результат равен 0.

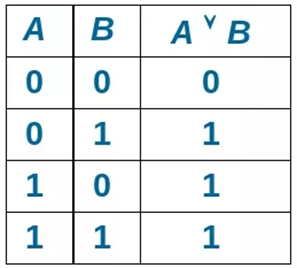

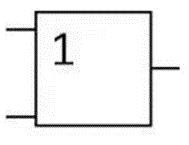

Дизъюнкция – функция двух, трех и более переменных, выполняет логическое сложение и работает по правилу: результат равен 0, если все операнды равны 0, во всех остальных случаях результат будет равен 1.

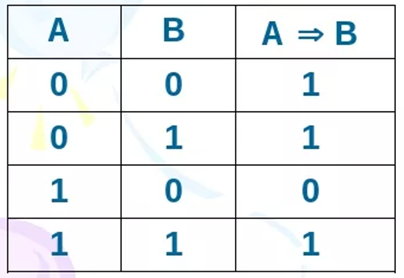

Импликация – функция двух переменных, которые могут принимать значение из множества (0,1), при этом результат так же принадлежит множеству (0,1) и работает по правилу: функция ложная лишь тогда, когда посылка истина, а следствие ложное.

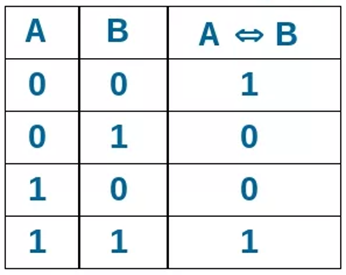

Эквивалентность – логическое выражение, которое является истинным тогда, когда оба простых логических выражения имеют одинаковую истинность.

Приведем таблицу истинности для перечисленных выше логических операций.

На рисунке 5 представим таблицу истинности для инверсии.

Рисунок 5 – Таблица истинности «Инверсия»

На рисунке 6 представим таблицу истинности для конъюнкции.

Рисунок 6 – Таблица истинности «Конъюнкция»

На рисунке 7 представим таблицу истинности дизъюнкции.

Рисунок 7 – Таблица истинности «Дизъюнкция»

На рисунке 8 представим таблицу истинности импликации.

Рисунок 8 – Таблица истинности «Импликация»

На рисунке 9 представим таблицу истинности эквивалентности.

Рисунок 9 – Таблица истинности «Эквивалентность»

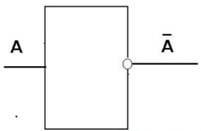

Условные обозначения элементов, приведенных выше логических операций, представим на рисунке 10.

а) б) в) г) д)

Рисунок 10 – Логические элементы

На рисунке представлены:

а) – инверсия; б) – конъюнкция; в) – дизъюнкция; г) – импликация; д) – эквивалентность.

2.3.5 Команды пересылки

Команды пересылки предназначены для операций над словами и строками. Основными командами являются команды MOV и MOVS.

Команда MOV пересчитывает 1 байт или слово из памяти в регистр, из регистра в память или из регистра в регистр. Она имеет следующий синтаксис:

MOV <получатель>,<источник>

При использовании данной команды необходимо учитывать следующие правила:

˗ оба операнда должны иметь одинаковую длину;

˗ в качестве одного из операндов обязательно должен использоваться регистр;

˗ нельзя пересылать непосредственно заданное значение в сегментный регистр.

Команда MOVS предназначена для работы над строками, которые представляют собой последовательность байт. В данной команде в качестве операнда могут использоваться регистры разной длины, но при этом должно выполняться следующее правило: содержимое исходного операнда копируется в больший по размеру регистр получателя данных.

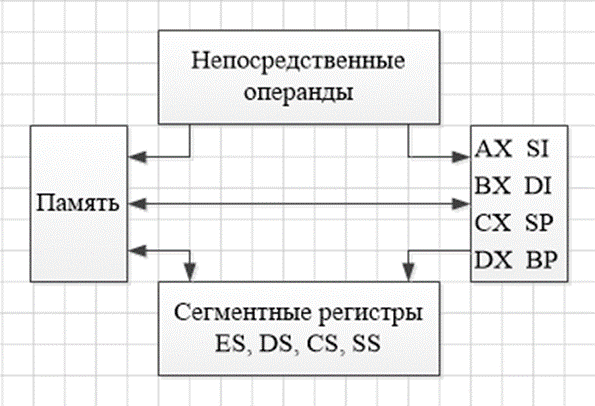

На рисунке 11 представим различные способы, которыми в процессе можно пересылать данные из одного места в другое.

Рисунок 11 – Пути пересылки данных

2.4 Разработка управляющего устройства

Для обеспечения работы всех устройств и узлов вычислительной машины в соответствии с заданной программой обеспечивается центральным устройством управления (ЦУУ), которая вырабатывает управляющие сигналы необходимые для выполнения.

Основными функциями устройства управления являются:

˗ определение очередности выборки команд из оперативной памяти;

˗ формирование физических адресов операндов;

˗ формирование сигналов для выполнения арифметических, логических и иных операций при выполнении программы;

˗ операция пуска и остановки вычислительного устройства;

˗ обеспечение работы вычислительного устройства в различных режимах.

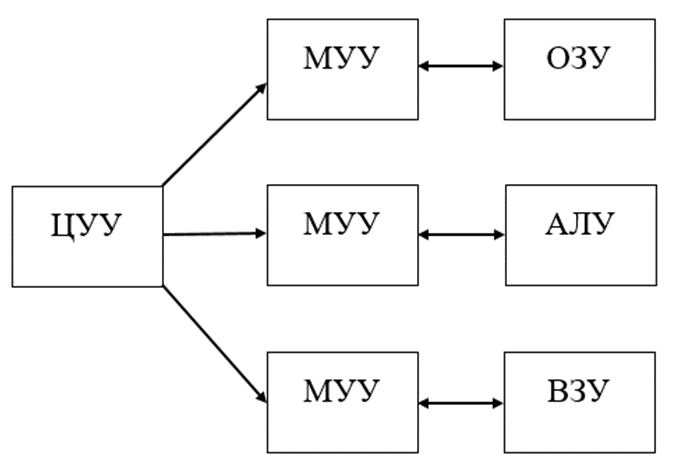

На рисунке 12 представим структурную схему управляющего устройства.

Рисунок 12 – Структурная схема управляющего устройства

ЦУУ – центральное устройство управления, которое выполняет основные функции по реализации программ. Эти функции оно выполняет через МУУ – местное устройство управления, находящиеся при каждом из устройств, входящих в состав вычислительной машины. Оно реализует специальные алгоритмы, соответствующие принципам действия разных внешних устройств.

Последовательность управляющих сигналов, вырабатываемых устройством управления зависит от числа выполняемых арифметических, логических операций и формата используемых команд.

2.4.1 Разработка формата команд

Формат команды – это структура команды с разметкой номеров разрядов, определяющих границы отдельных полей команды.

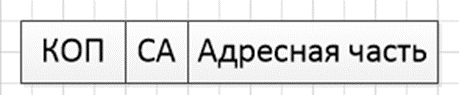

Структура любой команды состоит из нескольких полей, основные из которых представим на рисунке 13.

Рисунок 13 – Структура команды

Код операции (КОП) указывает какая именно операция (арифметическая, логическая и т.п.) выполняется. В адресной части команды указываются адреса операндов. В зависимости от структуры адресной части различают следующие типы команд:

-

безадресные; -

одноадресные -

двухадресные; -

трехадресные; -

четырехадресные.

Безадресная структура фиксирует адреса обоих операндов и результата операции, например, при работе со стековой памятью.

Одноадресная структура. Подразумеваемые адреса имеют результат операции и один из операндов. При этом один из операндов и результат операции размещаются в одном фиксированном регистре. Выделенный для этой цели внутренний регистр процессора получил название аккумулятор. Адрес другого операнда указывается в команде.

Двухадресная структура. Используется в вычислительных машинах, построенных так, что результат операции будет всегда помещаться в фиксированный регистр процессора, например, на место первого операнда.

Трехадресная структура. Используется в вычислительных машинах, построенных так, что после выполнения команды по адресу K (команда занимает L ячеек памяти) выполняется команда по адресу K+L. Такой порядок выборки команд называется естественным. Он нарушается только специальными командами передачи управления. При естественном порядке выборки адрес следующей команды формируется в устройстве, называемом счетчик адреса команд. В этом случае команда становится трехадресной.

Четырехадресная структура. Содержит наиболее полную информацию о выполняемой операции, включает поле кода операции и четыре адреса для указания ячеек памяти двух операндов, ячейки результата операции, и ячейки, содержащей адрес следующей команды. Такой порядок выборки команд называется принудительным. Он использовался в первых моделях вычислительных машин, имеющих небольшое число команд и очень незначительный объем ОП, поскольку длина такой команды зависит от разрядности адресов операндов и результата.

Общую длину команды определим по формуле:

где Rк – количество бит, отводимое под команду;

RAi – количество разрядов для записи i – того адреса;

l – количество адресов в команде;

RКОП – разрядность поля кода операции;

RCA – разрядность поля способа адресации.

Так как система команд разрабатываемого устройства предполагает 22 различных операций, то минимальную разрядность поля кода операции определим по формуле:

где int – округление в большую сторону до целого;