Файл: Лабораторная работа 2 исследование триггеров на интегральных микросхемах цель работы.doc

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 23.11.2023

Просмотров: 65

Скачиваний: 6

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Кафедра ЭПА и ЭО

Отчёт

Лабораторная работа №2

ИССЛЕДОВАНИЕ ТРИГГЕРОВ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ

Цель работы:

Экспериментальное исследование работы триггеров, выполненных на интегральных микросхемах, и закрепление знаний по последовательностной цифровой логике.

Порядок выполнения работы

-

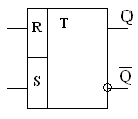

RS триггер.

Схема исследований RS триггера

Назначение RS триггера:

RS триггер можно использовать для запоминания информации, логические устройства электроприводов, в электронных часовых устройствах, в любых устройствах вычислительной техники.

Таблица № 1

| Режим Работы | Теория | Эксперимент | ||||||

| | | Q | | | | Q | | |

| Запрещенное состояние | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| Установка 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| Установка 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| Хранение | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 |

Диаграмма напряжений для RS триггера

Вывод:

Работа RS триггера соответствует своему назначению.

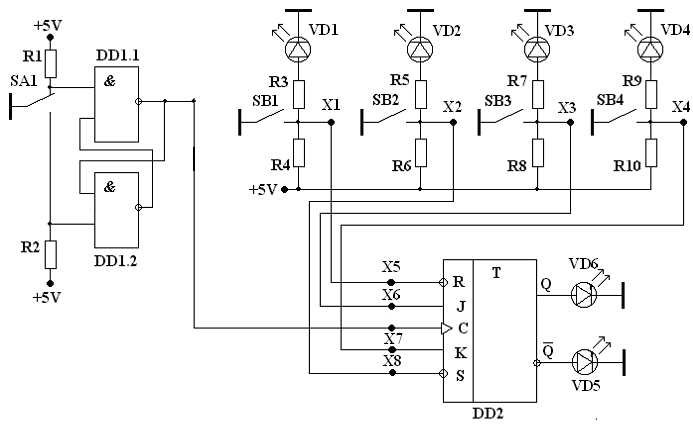

2) JK триггер.

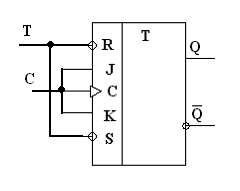

Схема исследований JK триггера

Назначение JK триггера:

JK триггер можно использовать для запоминания информации и ее записи, логические устройства электроприводов, в электронных часовых устройствах, в любых устройствах вычислительной техники.

Таблица № 2

| Режим Работы | Теория | Эксперимент | ||||||||

| J | K | C | Q | | J | K | C | Q | | |

| Запись 1 в JK-триггер | 1 | 0 |  | 1 | 0 | 1 | 0 |  | 1 | 0 |

| Запись 0 в JK-триггер | 0 | 1 |  | 0 | 1 | 0 | 1 |  | 0 | 1 |

| Триггер не ме-няет состояния | 0 | 0 |  | 0 | 1 | 0 | 0 |  | 0 | 1 |

| Триггер ме-няет состояние на инверсное | 1 | 1 |  | 1 | 0 | 1 | 1 |  | 1 | 0 |

Диаграмма напряжений для JK триггера

Вывод:

Работа JK триггера соответствует своему назначению.

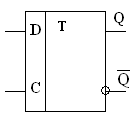

-

D триггер.

Схема исследований D триггера

Назначение D триггера:

D триггер можно использовать для запоминания информации, логические устройства электроприводов, в электронных часовых устройствах, в любых устройствах вычислительной техники.

Таблица № 3

| Режим Работы | Вход | Выход | ||||

| | | С | D | Q | | |

| Установка 1 | 1 | 1 |  | 1 | 1 | 0 |

| Установка 0 | 1 | 1 |  | 0 | 0 | 1 |

X – безразличное состояние

Диаграмма напряжений для D триггера

Вывод:

Работа D триггера соответствует своему назначению.

-

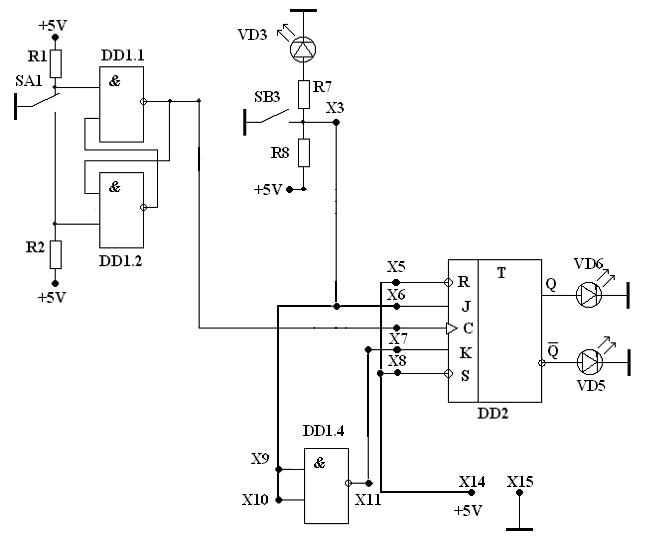

Т – триггер.

Т – триггер на основе JK – триггера:

Схема исследований Т триггера

Назначение T триггера:

T триггер можно использовать для запоминания информации, логические устройства электроприводов, в электронных часовых устройствах, в любых устройствах вычислительной техники.

Таблица № 4

| J | K | C | Q | |

| 1 | 1 |  | 1 | 0 |

| 1 | 1 |  | 0 | 1 |

Диаграмма напряжений для T триггера

Вывод:

Работа T триггера соответствует своему назначению.

Вывод по работе:

В данной работе были изучены логические основы триггеров и проведено экспериментальные исследование работы триггеров. Были изучены принцип работы, свойства триггеров, выполненных на интегральных микросхемах.