ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 23.11.2023

Просмотров: 101

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Решение. Для 16-битного счетчика максимальное время переполнения составляет

TT max =216x TG = 65536 x 1 мкс = 65536 мкс,

где 216 – максимальное число состояний 16-битного таймера.

Для формирования меньшего интервала времени в регистры таймера/счетчика следует загрузить начальное значение Code. Оно определяется из выражения T T =(2n – Code) TG.

Code = 2n – T T / TG =65536 – 3500/1=62036=hF254.

Тогда старший байт THx=0xF2, а младший байт TLx=0x54.

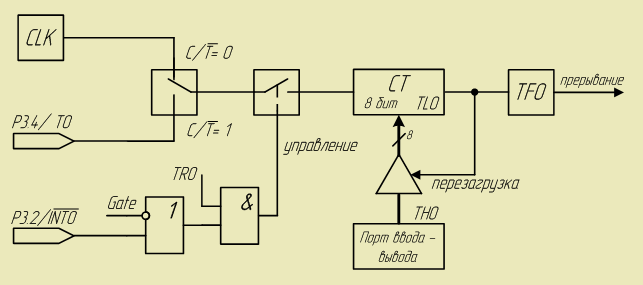

Режим 2 таймерного устройства обычно используется для формирования последовательности одинаковых интервалов времени. В режиме 2 регистр таймера TLx работает как 8-битный счетчик с автоматической перезагрузкой начального значения из регистра THx. Переполнение регистра TLx не только устанавливает флаг TFx, но и загружает регистр TLx содержимым регистра THx. Регистр THx предварительно инициализируется программно. Перезагрузка не изменяет содержимое регистра THx. Работе таймера в режиме 2 соответствует схема:

Рисунок 4.4 – Схема Таймера 0 в режиме 2

Перед первым запуском таймера должна быть выполнена инициализация: выбран режим работы таймера, способ запуска, источник тактирования. Для настройки таймера в регистр TCON следует записать соответствующее число.

Тема 5. Параллельные порты микроконтроллера ADuC842

5.1. Общие сведения

Каждый микроконтроллер имеет некоторое количество линий ввода-вывода, которые объединены в многоразрядные параллельные порты ввода-вывода.

В зависимости от реализуемых функций различают следующие типы параллельных портов:

-

однонаправленные порты, предназначенные только для ввода или только для вывода информации; -

двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе программно-управляемой настройки схемы; -

порты с альтернативной функцией, отдельные линии которых используются совместно со встроенными периферийными устройствами микроконтроллера, такими как таймеры, аналого-цифровые преобразователи и т.д.

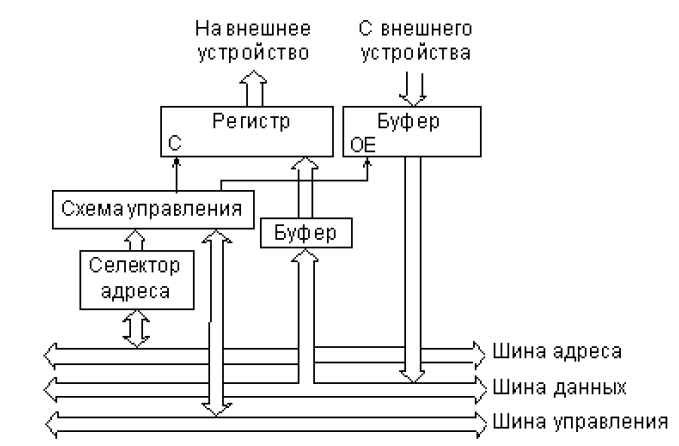

Обобщенная схема порта ввода-вывода имеет вид:

Рисунок 5.1 – Обобщенная схема порта ввода-вывода

При обращении со стороны магистрали селектор адреса распознает адрес, приписанный данному порту. Схема управления выдает внутренние стробы обмена в ответ на магистральны стробы обмена. Выходной буфер данных обеспечивает электрическое согласование шины данных с этим устройством (буфер может отсутствовать).

Данные из шины данных записываются в регистр по сигналу С и выдаются на внешнее устройство. Входной буфер данных передает входные данные с внешнего устройства на шину данных магистрали в цикле чтения из порта.

5.2. Порты микроконтроллера исходной архитектуры MCS-51

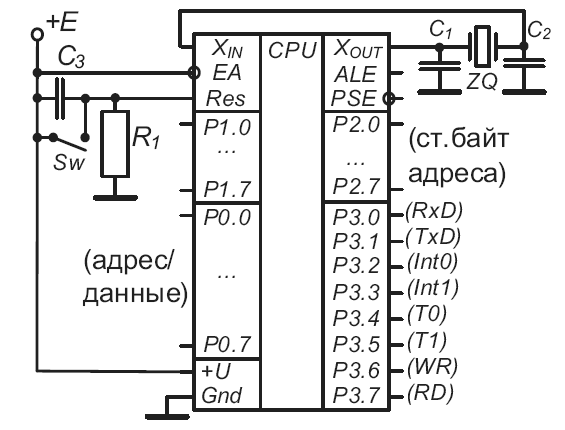

Условное графическое обозначение микроконтроллера приведено на рисунке 5.2.

Рисунок 5.2 – Условное графическое обозначение микроконтроллера

Все линии ввода-вывода микроконтроллера сгруппированы в четыре параллельных двунаправленных 8-разрядных порта Р0–Р3 (у микроконтроллера ADuC842 порт Р1 работает только на вход). Выводы портов можно использовать независимо друг от друга, побайтно или побитно, для ввода или вывода сигналов. Выводы отдельных битов портов нумеруются числами от 0 до 7 через точку после имени порта, например, Р1.5.

Основная функция портов – обмен данными. Помимо этого порты могут выполнять альтернативные функции, такие как обращение к внешней памяти, прием запросов прерываний и т.д. Альтернативные функции портов приведены на рисунке 5.2 в скобках.

При обращении к внешней памяти используются порты Р0 и Р2. Через порт Р0 выдается младший байт адреса и байт данных для записи или чтения. Через порт Р2 выдается старший байт адреса. Для обслуживания внешней памяти используются следующие внешние выводы:

ЕА (External Address – внешний адрес) – сигнал на этом выводе определяет, какое ПЗУ будет использоваться в работе, внешнее или внутреннее.

В большинстве случаев используется внутренняя память команд и этот инверсный сигнал пассивен и равен 1.

ALE (Address Latch Enable – «защелка» адреса разрешена) – выход, на котором формируется тактовый импульс для синхронизации внешних устройств, служит чаще всего для фиксации во внешнем регистре младшего байта адреса, выводимого через порт Р0.

PSE (Program Storage Enable) – инверсный выход, на котором образуется синхросигнал чтения из внешней памяти команд. Он возникает тогда, когда происходит выборка из внешнего ПЗУ

, определяя момент приема кода очередной команды через порт Р0.

Порт Р1 в базовой конфигурации альтернативных функций не имеет.

Биты порта Р3 могут использоваться различной внутренней аппаратурой:

RxD – вход приемника последовательного порта;

TxD – выход передатчика последовательного порта;

INT0, INT1 – (INTerrupt – прерывание) – входы внешних запросов на прерывание работы процессора по программе для экстренного обслуживания внешних устройств;

Т0, Т1 – внешние входы для управления таймерами-счетчиками;

RD (ReaD), WR (WRite) – выходы инверсных синхросигналов чтения и записи, которые формируются в момент, когда процессор обращается к внешнему ОЗУ, производя чтение или запись.

Служебные выводы общего назначения обеспечивают работоспособность микроконтроллера и служат для подключения внешних элементов для генератора и цепи сброса.

Xin, Xout – вход и выход внутреннего генератора для подключения внешнего кварцевого резонатора, задающего тактовую частоту работы микроконтроллера.

RES (от Reset – сбросить) – вход, который служит для установки микроконтроллера в начальное состояние. При этом большинство битов спецрегистров сбрасываются в ноль, а биты портов устанавливаются в единичное состояние (настраиваются на ввод информации). В программный счетчик записывается нулевой код, и выполнение программы после окончания импульса сброса начинается с нулевой ячейки.

5.3. Особенности выходных цепей портов

При подключении внешних схем к микроконтроллеру нужно помнить, что выходные каскады портов в х51 имеют схемотехнику двух типов: классическую двунаправленную (с двумя ключами и третьим состоянием) и квазидвунаправленную (с одним ключом и внутренним резистором нагрузки).

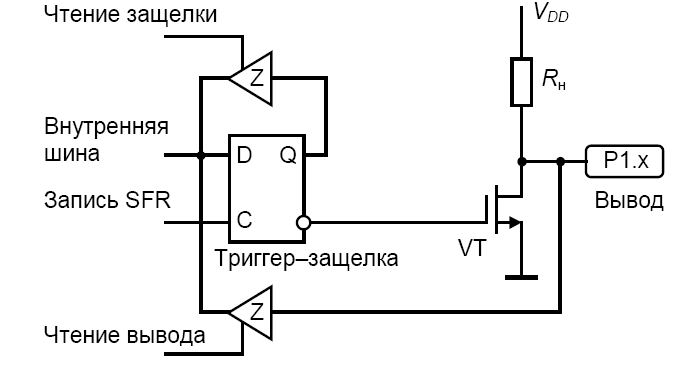

Рассмотрим структурные схемы аппаратных средств, обслуживающих одну линию портов Р0-Р3. Все линии параллельных портов имеют защедки типа D-триггера, которые объединены в группы по 8 и рассматриваются как регистры специальных функций Р0-Р3. Кроме защелки каждая линия ввода-вывода имеет входной буфер и формирователь выходного сигнала. Формирователи выходного сигнала портов Р1-Р3 выполнены на полевых транзисторах с внутренней нагрузкой, в то время как формирователи порта Р0 – на транзисторах с открытым стоком.

Схема функционирования одной линии ввода-вывода портов Р1-Р3 представлена на рисунке 5.3. Запись входных данных в защелку происходит

Рисунок 5.3 – Схема линии ввода-вывода портов Р1-Р3

по высокому уровню синхросигнала С. Из рисунка 5.3 видно, что на внутреннюю шину микроконтроллера может быть прочитано как состояние защелки, так и значение сигнала на внешнем выводе.

При использовании линии для вывода данных необходимо записать выводимое значение сигнала «0» или «1» в триггер-защелку. Этот сигнал затем появляется на внешнем выводе микросхемы.

Для использования линии порта в качестве входа ее защелка должна содержать «1». При этом выходной внутренний транзистор закрывается. На выводе микроконтроллера за счет внутреннего подтягивающего резистора устанавливается высокий уровень напряжения. Этот уровень может быть изменен внешним источником на нулевой потенциал. Это дает возможность микроконтроллеру правильно воспринимать входные данные. В случае же, когда в разряд порта записан лог. 0, внутренний транзистор открыт. На выходе появляется низкий потенциал, изменить который извне невозможно. Поэтому перед вводом информации через параллельный порт соответствующий разряд необходимо настроить на ввод – записать в него лог. 1. Из-за такого механизма работ порты Р1-Р3 называют «квазидвунаправленными».

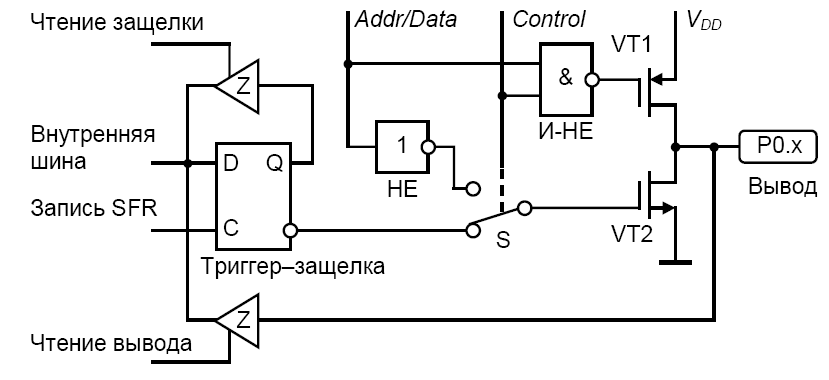

Порт Р0 элементов постоянного подтягивания к уровню «1» не имеет (рисунок 5.4). Верхний транзистор (VT1) выходного формирователя открыт

Рисунок 5.4 – Схема линии ввода-вывода порта Р0

только при выдаче лог.1 на линию в качестве бита адреса внешней памяти. При выполнении основной функции по обмену данными инверсный выход триггера соединен с затвором транзистора VT2. При закрытом резисторе VT1 для работы выходного ключа на транзисторе VT2 необходимо включить внешний подтягивающий резистор.

При записи данных в порт внутренним сигналом «Запись SFR» данные с линии внутренней шины записываются в триггер и появляются на выводе Р0.х.

Чтение данных с вывода порта на линию внутренней шины данных выполняется сигналом «Чтение вывода» при закрытом транзисторе VT2. Для запирания транзистора VT2 и перевода разряда порта в режим чтения необходимо записать в его триггер лог.1. Запись «1» в защелку порта Р0 переводит линию в высокоимпедансное состояние (транзисторы VT1 и VT2 закрыты). Поэтому этот порт является действительно двунаправленным.

Тема 6. Система прерываний микроконтроллера

6.1. Общие сведения

Назначение системы прерываний – реагировать на определенные события путем прерывания работы процессора по выполнению программы и переключения процессора на выполнение другой программы, обслуживающей соответствующую ситуацию. Запросы прерывания могут поступать как от внешних источников, так и от источников внутренних модулей микроконтроллера.

В качестве входов для приема запросов от внешних источников чаще всего используются выводы параллельных портов ввода-вывода, для которых эта функция является альтернативной. Источниками запросов внешних прерываний также могут быть любые изменения внешних сигналов на некоторых специально выделенных линиях портов ввода-вывода.

Источниками внутренних запросов прерываний могут служить следующие события: переполнение таймеров/счетчиков, завершение приема или передачи информации по одному из последовательных портов и другие.

Любой запрос прерывания поступает на обработку, если прерывания в микроконтроллере разрешены, и разрешено прерывание по данному запросу. Адрес, который загружается в программный счетчик при переходе к обработке прерывания, называется «вектором прерывания». Различные источники прерываний могут иметь разные векторы или использовать некоторые из них совместно.

Классический микроконтроллер MCS-51 имеет пять источников прерываний (рисунок 6.1): два внешних прерывания, инициированных сигналами на входах INT0 (вывод Р3.2) и INT1 (вывод Р3.3), два прерывания таймеров (Таймера 0 и Таймера 1), прерывание последовательного порта.

Внешние прерывания INT0 и INT1 могут быть вызваны уровнем или переходом сигнала из 1 в 0 (срезом) на входах микроконтроллера в зависимости от значений управляющих битов IT0 и IT1 в регистре TCON. От внешних прерываний устанавливаются флаги IE0 и IE1 в регистре TCON, которые инициируют вызов соответствующей подпрограммы обслуживания

Рисунок 6.1 – Схема системы прерываний 8051

прерывания. Сброс этих флагов выполняется аппаратно только в том случае, если прерывание было вызвано по срезу сигнала. Если же прерывание вызвано уровнем входного сигнала, тог сбросом флага IE управляет соответствующая подпрограмма обслуживания прерывания путем воздействия на источник прерывания с целью снятия им запроса.