ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 23.11.2023

Просмотров: 104

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Флаги запросов прерываний от таймеров TF0 и TF1сбрасываются автоматически при передаче управления подпрограмме обслуживания.

Флаги запросов прерываний RI и TI устанавливаются аппаратно, а сбрасываться должны программой. Прерывания от последовательного порта при передаче и приеме вызывают одну и ту же подпрограмму обслуживания. В ней, опросив флаги, можно определить источник прерываний.

Прерывания могут быть вызваны или отменены программой, т.к. все перечисленные флаги программно доступны.

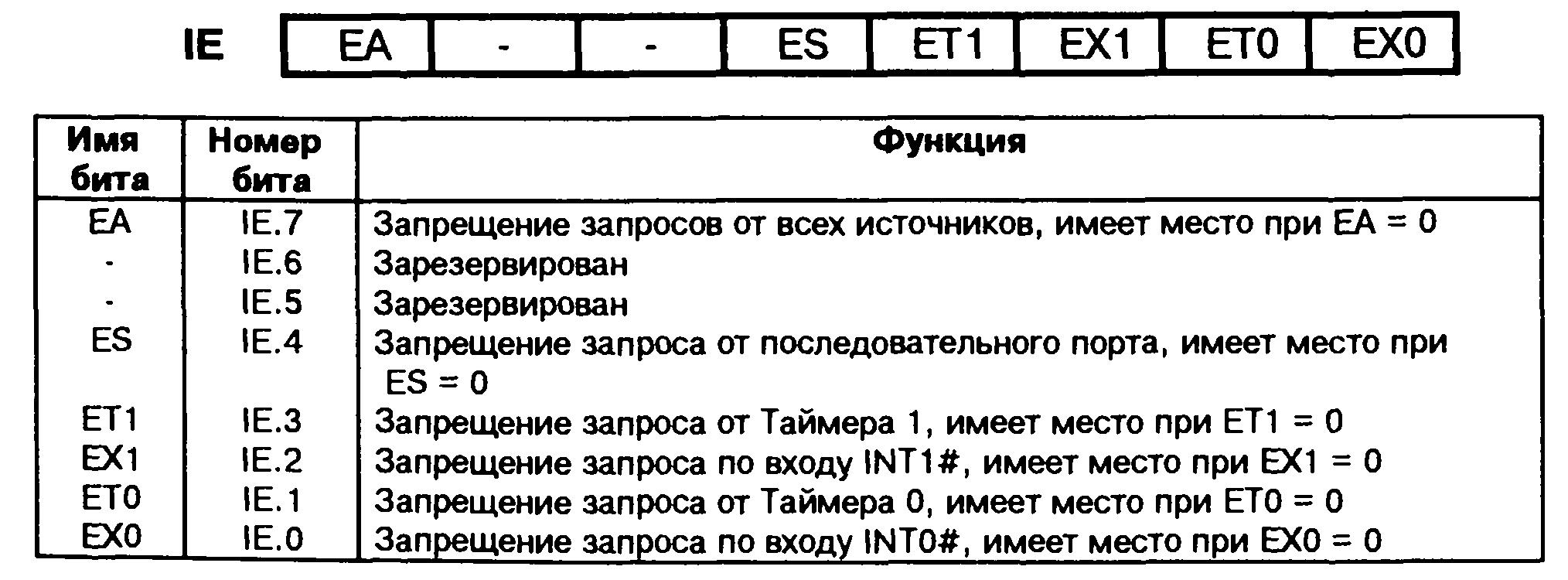

В блоке регистров специальных функций есть два регистра, предназначенных для управления режимом прерываний и уровнями приоритета. Форматы этих регистров, имеющих символические имена IE и IP, описаны ниже.

Любое из прерываний будет вызвано только в том случае, если его вызов разрешен путем установки соответствующих битов регистра IE (рисунок 6.2). Здесь бит ЕА разрешает работу системы прерываний микроконтроллера, а для разрешения запроса прерывания для каждого конкретного источника должен быть установлен соответствующий бит.

Рисунок 6.2 – Структура и назначение бит регистра IE

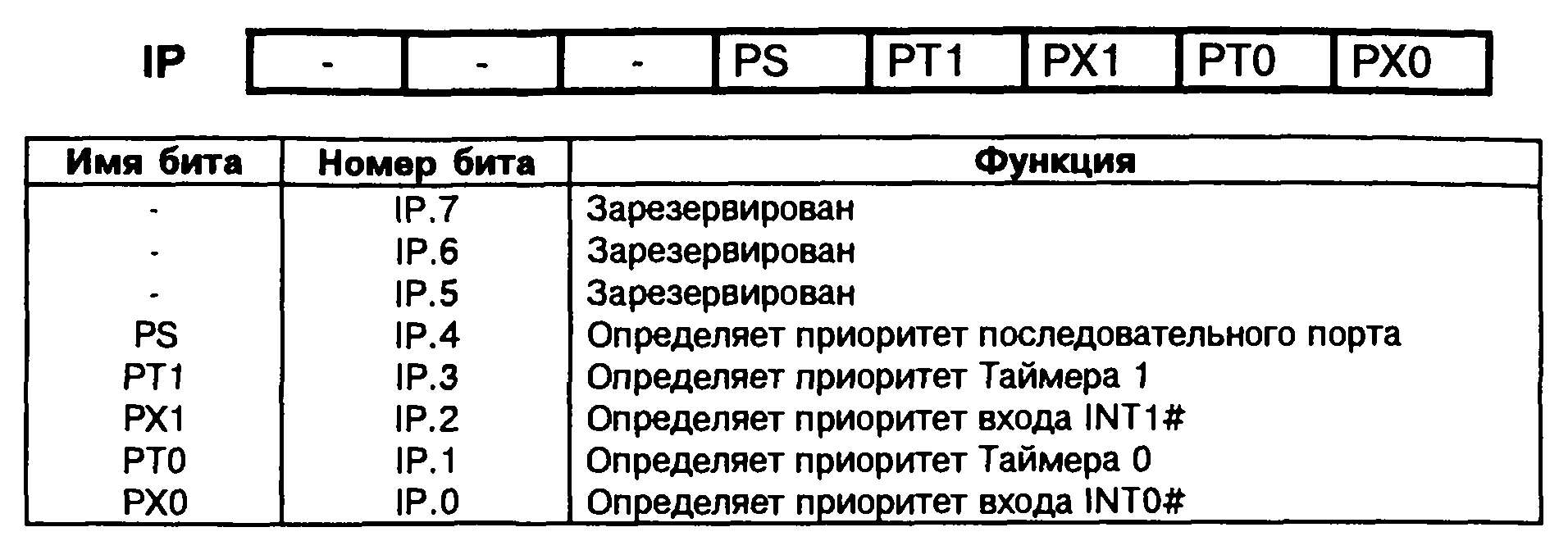

Очередность выполнения двух и более одновременно поступивших прерываний определяется их приоритетами. Для изменения приоритетов выполнения прерываний следует устанавливать специальные биты в регистре приоритетов IP (рисунок 6.3).

Рисунок 6.3 – Структура и назначение бит регистра IP

В архитектуре MCS-51 имеет место двухступенчатый механизм определения приоритетов. На первой ступени приоритеты имеют два уровня: «высокий» и «низкий», определяемые значениями битов регистра IP.

При одновременном появлении нескольких запросов одного уровня очередность обслуживания определяется путем последовательного опроса (указана стрелкой на рисунке 6.1).

Реакция системы прерываний на любой запрос, разрешенный к обслуживанию, заключается в передаче управления от текущей программы процедуре обслуживания прерывания данного типа. Эта передача осуществляется посредством аппаратно сформированной команды LCALL. При этом текущая команда выполняется до конца. Команда LCALL сохраняет текущее значение счетчика команд РС (адрес следующей команды) в стеке, а в РС загружает адрес-вектор. Сохранение в стеке других регистров микроконтроллера осуществляется командами PUSH в начале процедуры обслуживания. В конце процедуры должны стоять соответствующие команды выгрузки POP. Процедура обслуживания прерывания завершается командой RETI, которая выгружает из стека адрес возврата и помещает его в РС.

Ввиду того, что адреса векторов прерываний расположены в памяти с интервалом 8 ячеек, по ним, как правило, размещают не сами процедуры обслуживания, а команды безусловного перехода на полпрограммы. В этом случае имеет место так называемая таблица переходов системы прерываний.

Таким образом, для того, чтобы программа обработки прерывания могла выполняться, необходимо три условия:

-

наличие программы-обработчика прерывания, размещенной по определенному адресу в начальной области памяти программ; -

установка в регистре IE бита разрешения всех прерываний (EA) в «1»; -

установка соответствующих битов в регистре разрешения прерываний и, при необходимости, в регистре приоритетов.

6.2. Обозначение программы-обработчика прерываний

В языке Keil C51 для определения функции, как обработчика прерывания, используется ключевое слово interrupt:

void mInitProc() interrupt mNomerInt using mBank{

… // Здесь размещается текст прерывающей процедуры

}

В качестве номера прерывания mNomerInt подставляют константы от 0 (внешнее прерывание 0) до 4 (прерывание от последовательного порта) для базового микроконтроллерного семейства MCS-51. Ключевое слово using, указывающее номер используемого регистрового банка памяти mBank (от 0 до 3), чаще всего опускают, позволяя компилятору самому определить его. Вот пример определения программы-обработчика прерывания Таймера 0 (номер прерывания 1):

void timer0ISR(void) interrupt 1 using 1{

…

}

При написании программ-обработчиков прерываний следует учитывать следующие особенности:

-

никакие параметры в программу-обработчик не передаются. Компилятор выдаст ошибку, если подобное будет обнаружено; -

функции-обработчики прерываний не возвращают значений, поэтому объявляются с атрибутом void; -

функцию-обработчик прерывания нельзя вызывать напрямую из программы, поскольку это может привести к краху системы из-за разрушения содержимого программных регистров, счетчика команд и стека.

6.3. Результат работы прерывающих процедур

Как было указано выше, функции прерывания не должны иметь аргументов и возвращать значения. Они могут только изменять ранее определенные переменные, но делают это неожиданно для основной программы и остальных процедур. Вследствие этого изменения общих переменных или портов ввода/вывода, производимые в ходе прерывания, могут оказаться какое-то время незамеченными. Поэтому. Чтобы заставить компилятор каждый раз считывать значение такой переменной (т.е. запретить сохранение ее во временном регистре). Обязательно нужно использовать при описании подобных переменных модификацию

volatile.

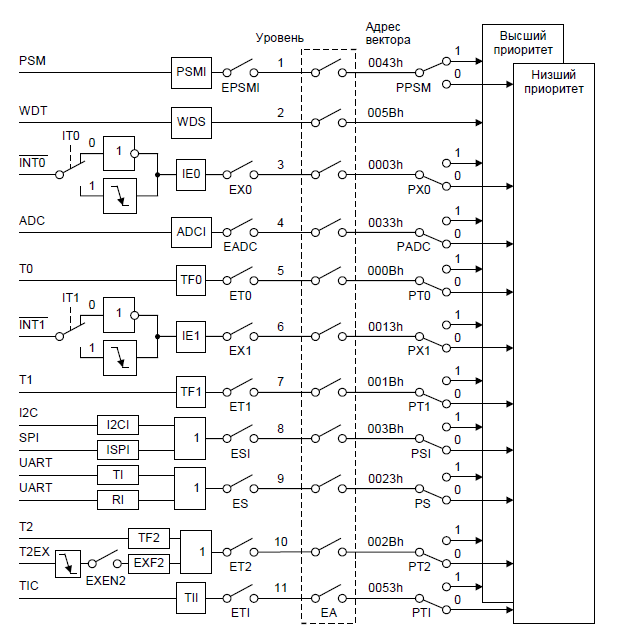

6.4. Особенности системы прерываний микроконтроллера ADuC842

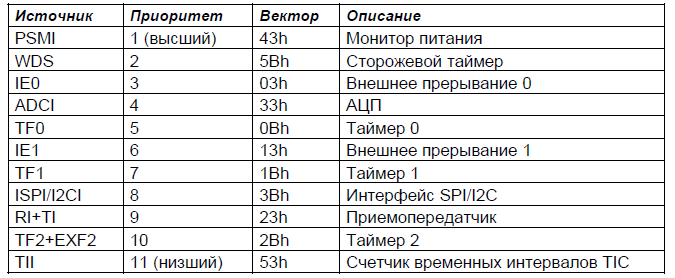

Схема прерываний микроконтроллера ADuC842 изображена на рисунке 6.4. В системе 11 уровней прерываний и 14 источников прерываний. Для управления системой

Рисунок 6.4 – Схема системы прерываний ADuC842

прерываний используются регистры IE, IP и IEIP2.

Разряды регистра IE (Interrupt Enable) управляют разрешением основных прерываний. Дополнительно к битам исходной архитектуры MCS-51 (рисунок 6.2) добавлены: EADC – бит разрешения прерывания АЦП (шестой разряд) и ET2 – бит разрешения прерываний по переполнению Таймера 2 (пятый разряд).

Каждому уровню прерывания соответствует один из двух уровней приоритета – низший и высший. Текущий приоритет данного уровня определяется регистром IP. Дополнительно к битам исходной архитектуры MCS-51 (рисунок 6.3) добавлены: PADC – бит приоритета прерывания АЦП (шестой разряд) и PT2 – бит приоритета прерывания Таймера 2 (пятый разряд).

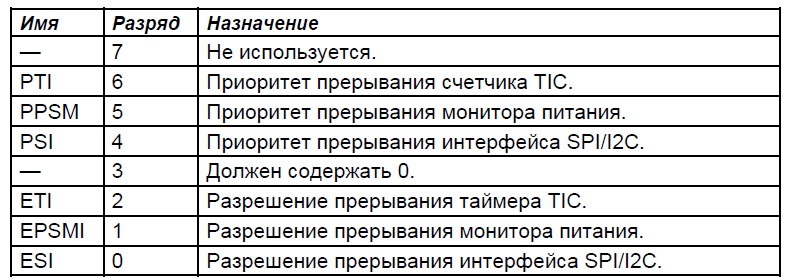

Для разрешения прерываний и задания приоритетов в микроконтроллере используется также дополнительный регистр IEIP2. Структура и назначение его битов приведены на рисунке 6.5.

Рисунок 6.5 – Структура и назначение бит регистра IEIP2

Начальное значение регистра IEIP2 равно A0h.

События, приводящие к возникновению прерываний, могут возникать в произвольные моменты времени. Однако момент возникновения прерывания привязан к окончанию машинного цикла, завершающего исполнение машинной инструкции (прерывания откладываются до окончания исполнения текущей команды).

Прежде всего система прерываний определяет, не находится ли она в состоянии блокировки. Блокировка устанавливается в момент входа в прерывание, то есть в начале обслуживания прерывания. При этом могут возникать различные ситуации из-за наличия прерываний разных приоритетов.

Если система находится в состоянии блокировки по прерыванию от события низшего приоритета, то прерывание разрешается (возникает), если событие имеет высший приоритет, и запрещается (откладывается), если событие имеет низший приоритет. Например, если система обслуживает окончание приема байта по последовательному порту, которому назначен низший приоритет, и возникает переполнение таймера 0, также имеющее низший приоритет, то прерывание по переполнению таймера откладывается. Если же таймеру 0 назначен высший приоритет, то обслуживание приемопередатчика приостанавливается, и возникает прерывание по переполнению таймера 0.

Если система находится в состоянии блокировки по прерыванию от события, имеющего высший приоритет, то никакое событие, независимо от его приоритета, не может привести к повторному прерыванию.

К моменту окончания исполнения текущей машинной инструкции возможно также возникновение двух и более прерываний, которые считаются одновременными. В этом случае из множества прерываний возникает то, которое имеет более высокий уровень, с учетом приоритетов. Сначала проверяется наличие запроса на прерывание высшего приоритета, затем низшего. Блокировка прерываний в этом случае также имеет место и влияет на обслуживание или откладывание прерывания.

На рисунке 6.6 приведен порядок опроса прерываний одного уровня.

Рисунок 6.6 – Порядок опроса прерываний одного уровня

Отложенное прерывание ожидает момента, когда блокировка будет снята. Блокировка снимается инструкцией RETI, которая обязательно должна завершать подпрограмму обслуживания прерывания.

Тема 7. Аналого-цифровой преобразователь микроконтроллера

7.1. АЦП последовательного приближения

Обработка поступающих в микроконтроллер аналоговых сигналов осуществляется при помощи устройств, называемых аналого-цифровыми преобразователями, или сокращенно АЦП. Многие современные микроконтроллеры имеют встроенные АЦП.

В настоящее время широкое применение находят АЦП последовательного приближения. Данный тип чаще всего используется в разнообразных измерительных приборах и в системах сбора данных. Преимуществами этих преобразователей являются достаточно высокая разрядность (разрешение 12, 14 или 16 бит), приемлемая скорость преобразования (десятки и сотни киловыборок в секунду), а также невысокая цена и низкое энергопотребление. В настоящий момент АЦП последовательного приближения позволяют измерять напряжение с точностью до 16 разрядов с частотой дискретизации более 100 киловыборок в секунду.

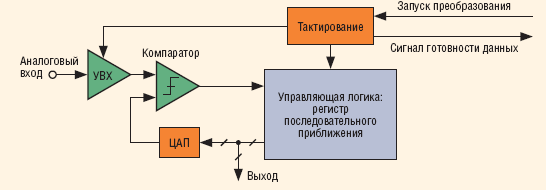

Базовая схема АЦП последовательного приближения показана на рисунке 7.1.

Рисунок 7.1 – Базовая схема АЦП последовательного приближения

Для обработки быстро изменяющихся сигналов на входе АЦП имеется устройство выборки-хранения (УВХ). На выходе этого устройства сигнал остается постоянным во время всего цикла преобразования. Преобразование начинается с установки выходного напряжения встроенного цифроаналогового преобразователя (ЦАП) на середину диапазона. Компаратор сравнивает выходное напряжение УВХ с выходным напряжением ЦАП. Результат сравнения (он является старшим битом выходного кода) записывается в регистр последовательного приближения (РПП) как 0 или 1. Затем, в зависимости от значения старшего бита, на выходе ЦАП устанавливается напряжение, равное 1/4 или 3/4 диапазона, и компаратор определяет значение следующего бита. Результат записывается в регистр, и процесс продолжается до тех пор, пока не будут определены значения всех битов. После окончания преобразования устанавливается логический сигнал готовности (BUZY). В англоязычной литературе аббревиатура SAR (successive-approximation register, регистр последовательного приближения) обычно понимается как название для всей архитектуры.

Принцип преобразования, используемый в работе преобразователя и заключающийся в последовательном сравнении измеряемой величины с 1/2, 1/4, 1/8 и т.д. от