ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 23.11.2023

Просмотров: 99

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

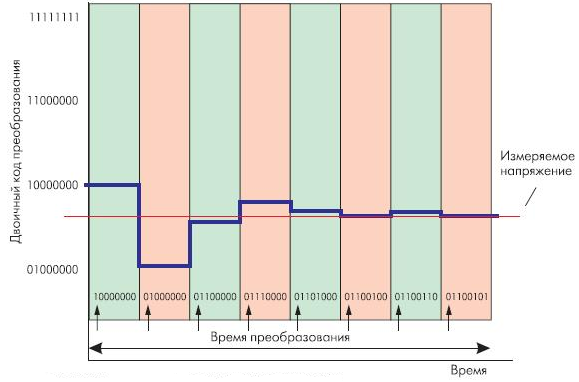

возможного максимального ее значения, носит название принципа дихотомии. В связи с этим для n-разрядного АЦП весь процесс преобразования занимает n последовательных шагов (итераций).

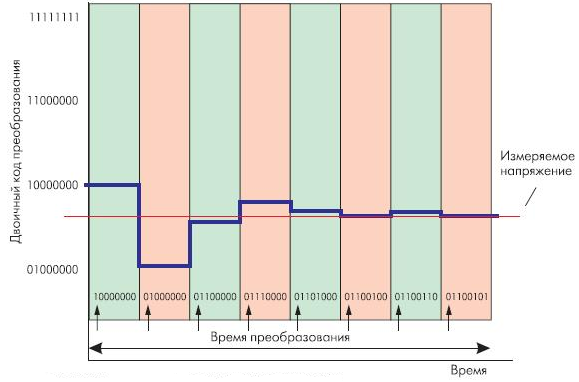

Функционирование схемы иллюстрирует временная диаграмма работы 8-разрядного преобразователя, представленная на рисунке 7.2.

Рисунок 7.2 – Преобразование в АЦП последовательного приближения

В начале цикла преобразования все выходы РПП принудительно устанавливаются в логический 0 за исключением старшего разряда. Это формирует на выходе ЦАП сигнал, значение которого равно «10000000». Если входное напряжение меньше половины входного диапазона АЦП, тогда выход компаратора примет значение логического 0. Это дает регистру последовательного приближения команду переключить свои выходы в состояние «01000000», что соответственно приведет к изменению выходного напряжения ЦАП, подаваемого на компаратор. Если при этом выход компаратора по-прежнему оставался бы в нуле, то выходы регистра переключились бы в состояние «00100000». Но на этом такте преобразования выходное напряжение ЦАП меньше, чем входное напряжение, и компаратор переключается в состояние логической 1. Это предписывает регистру последовательного приближения сохранить «1» во втором разряде и подать «1» на третий разряд. Описанный алгоритм работы затем вновь повторяется до последнего разряда.

7.2. Аналого-цифровой преобразователь микроконтроллера ADuC842

Микроконтроллер ADuC842 включает в свой состав блок АЦП, содержащий 9-канальный мультиплексор, встроенный источник опорного напряжения (ИОН), устройство выборки-хранения, схему калибровки и 12-разрядный АЦП последовательного приближения с однополярным питанием.

Мультиплексор служит для подключения одного из источников аналоговых сигналов (ADC0-ADC7) ко входу АЦП. Выбор источника сигнала для преобразования осуществляется посредством записи номера канала в соответствующие разряды регистра управления АЦП.

Преобразователь воспринимает входные аналоговые сигналы в диапазоне от 0 до +UREF. Может использоваться опорное напряжение U

REF, формируемое встроенным источником (ИОН), либо подаваемое от внешнего источника.

Режимы преобразования (однократный или циклический) могут быть установлены программно. Кроме того, преобразование может быть инициализировано внешним сигналом запуска на выводе CONVST. Для запуска повторяющегося процесса преобразования можно использовать сигнал Таймера

2.

Преобразователь можно установить в режим передачи данных по каналу прямого доступа к памяти (DMA). При этом блок повторяет циклы преобразования и посылает выборки во внешнюю память данных, минуя процессор.

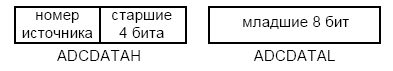

Для управления АЦП используются три управляющих регистра ADCCON1, ADCCON2, ADCCON3, два регистра данных ADCDATAH и ADCDATAL, два регистра калибровочного коэффициента по усилению ADCGAINL и ADCGAINH, а также регистры калибровочного коэффициента по смещению нуля ADCOFSL и ADCOFSH.

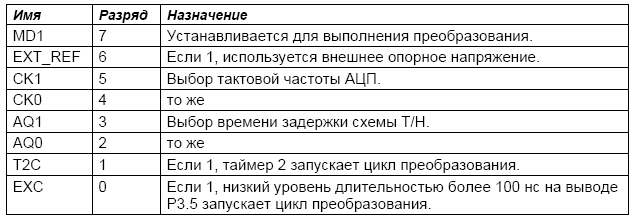

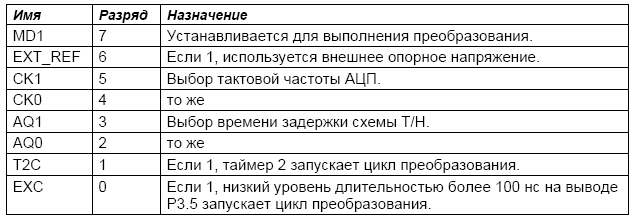

Регистр ADCCON1 управляет запуском преобразования. Назначение разрядов регистра приведено в таблице 7.1.

Таблица 7.1. Регистр ADCCON1 управления АЦП

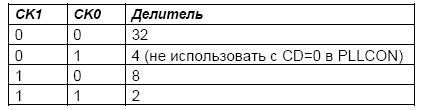

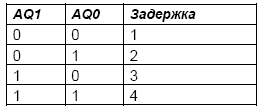

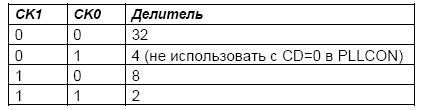

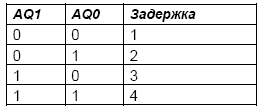

Запустить преобразование можно программно при помощи бита MD1, сигналом переполнения Таймера 2 и при помощи сигнала CONVST, который подается на вывод Р3.5. Дополнительно в этом регистре выбирается делитель для получения тактовой частоты преобразования СК (таблица 7.2) и время задержки для распространения сигнала AQ в тактах (таблица 7.3).

Таблица 7.2. Выбор тактовой частоты преобразования

Таблица 7.3. Выбор задержки сигнала

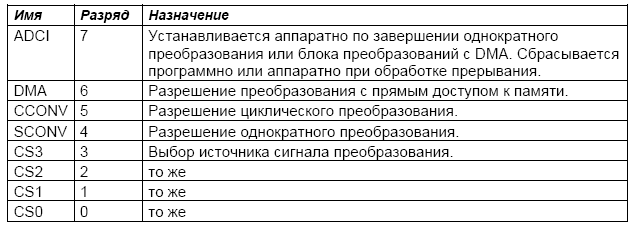

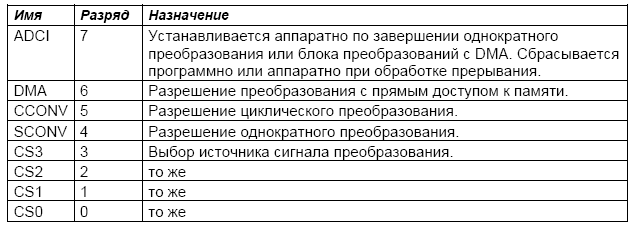

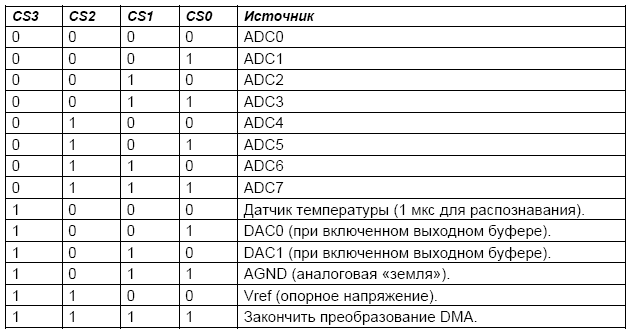

Регистр ADCCON2 предназначен для выбора источника сигнала, а также режима преобразования. Назначение разрядов регистра приведено в таблице 7.4.

Таблица 7.4. Регистр ADCCON2 управления АЦП

АЦП может выполнять однократные и циклические преобразования. Однократное преобразование выполняется при установленном бите SCONV (Single Conversion). По окончании преобразования устанавливается флаг прерывания ADCI. Время одного преобразования составляет 16 тактов частоты, поступающей на АЦП, плюс число тактов задержки (таблица 7.3).

Циклическое преобразование выполняется при установленном бите CCONV (Continuous Conversion). В этом режиме АЦП непрерывно преобразует входной аналоговый сигнал с частотой, установленной битами СК и AQ в регистре ADCCON1. Следует иметь в виду, что максимальная частота преобразования отводит управляющей программе на обслуживание одного преобразования всего 2 мкс (максимум 32 машинных цикла), включая время обслуживания прерывания. Поэтому АЦП может работать в режиме прямого доступа к памяти (DMA) , в котором результаты преобразования записываются во внешнюю память данных без участия процессора и обрабатываются позднее.

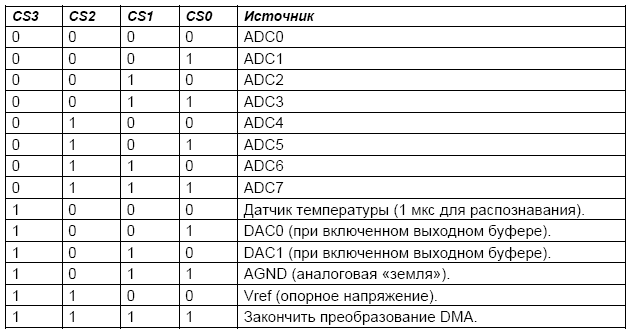

Таблица 7.5. Выбор источника аналогового сигнала

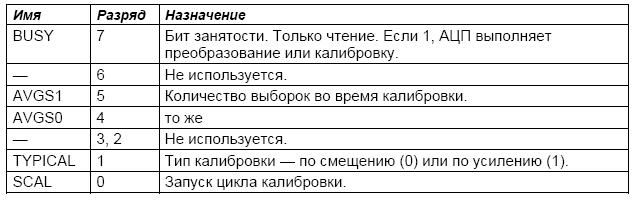

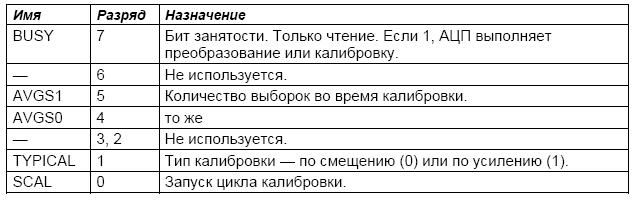

Регистр ADCCON3 используется для калибровки АЦП. Назначение разрядов регистра приведено в таблице 7.6.

Таблица 7.6. Регистр ADCCON3 управления АЦП

Микросхема поставляется потребителю откалиброванной. Это означает, что результат преобразования скорректирован для уменьшения влияния дрейфа (медленного изменения) постоянных токов в цепях АЦП.

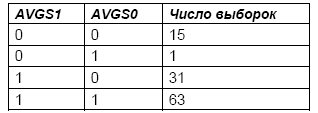

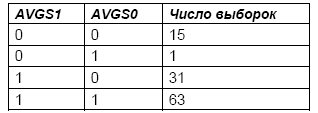

Тем не менее, при эксплуатации устройства может понадобиться его калибровка для повышения точности измерений. Вовремя цикла калибровки устанавливается преобразование аналогового нуля или опорного напряжения с тем, чтобы результат преобразования тоже был равен нулю или опорному напряжению. Калибровка выполняется несколькими выборками. Количество выборок определяется битами AVGSx по таблице 7.7.

За один цикл выполняется калибровка либо смещения нуля, либо коэффициента усиления передаточной характеристики. Выбор типа калибровки выполняется битом TYPICAL. Сначала должна выполняться калибровка нуля при подаче на вход сигнала нуля. Затем выполняется калибровка усиления с подачей на вход сигнала опорного напряжения UREF. Калибровочные коэффициенты имеют разрядность 14 бит.

Таблица 7.7. Выбор числа выборок калибровки

Преобразование аналогового сигнала в цифровой осуществляется в диапазоне от 0 до UREF, которое составляет 2,5 В при использовании внутреннего ИОН. При этом точность измерения составляет UREF / 212=0,61 мВ. Значение преобразования можно вычислить, если умножить точность преобразования на результат преобразования. Так, если результат преобразования равен 964, измеряемое напряжение равно 0,588 В. Максимальное значение преобразования 4095 соответствует опорному напряжению.

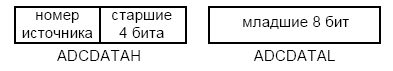

После программирования блока АЦП с использованием регистров ADCCON1 – ACCON3 он начинает выполнять преобразования аналоговых входных сигналов и формировать 12-разрядные выходные коды в регистрах ADCDATAH(L). В старшие четыре разряда регистра ADCDATAH записывается номер канала. Формат слова результата показан на рисунке 7.3.

Рисунок 7.3 – Формат слова результата АЦП

7.3. Разметка внешней памяти данных в режиме прямого доступа к памяти

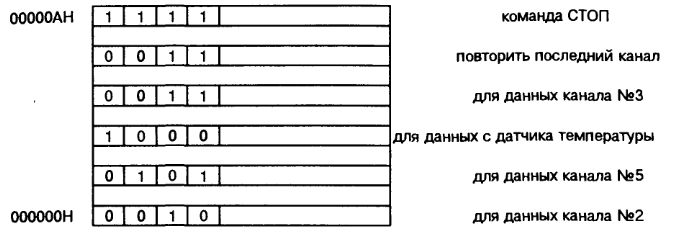

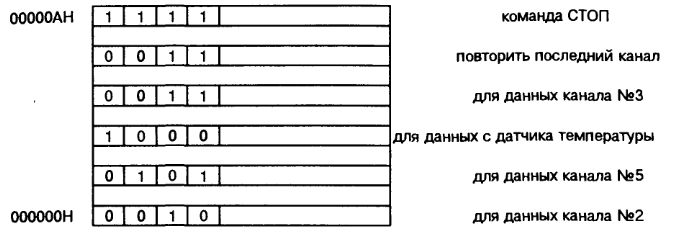

Режим прямого доступа к памяти обеспечивает реализацию максимального быстродействия АЦП. До включения режима DMA необходимо разметить внешнюю память, в которую будут записываться выборки. Разметка состоит в записи номеров каналов во внешнюю память. На рисунке 7.4 показана типовая разметка внешней памяти. После завершения разметки в регистры

Рисунок 7.4 – Разметка внешней памяти данных для режима DMA

DMAP, DMAH и DMAL заносится стартовый адрес DMA. В примере на рисунке 7.4 этот адрес равен h000000. Конец таблицы DMA указывается записью кода «1111» в поле номера канала. Теперь можно инициировать режим DMA установкой бита разрешения (ADCCON2.6, DMA).

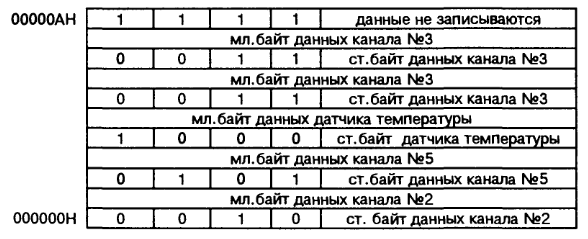

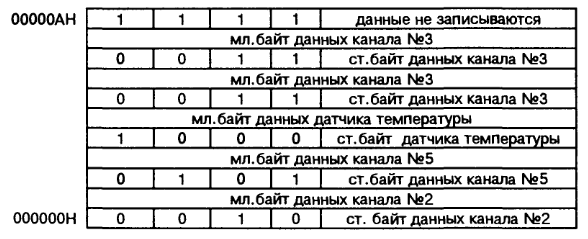

Режим DMA включается только в том случае, если пользователь предварительно установил время преобразования и режим запуска в регистрах ADCCON1 и ADCCON2. В конце цикла DMA устанавливается бит прерывания АЦП (ADCCON2.7, ADCI), а внешняя память данных оказывается загруженной результатами, как показано на рисунке 7.5. Результаты разметки сохраняются.

Рисунок 7.5 – Внешняя память данных после цикла DMA

Во время цикла DMA процессор свободен и может выполнять команды, однако доступ процессора к портам Р2 и Р0 (которые используются контроллером DMA) в это время запрещен. Это означает, что если при выполнении программы встретится обращение к портам Р2 и Р0, данные с внешних выводов прочитаны не будут. Как только блок данных DMA будет записан во внешнюю память, инициируется прерывание и процедура обслуживания может обработать данные уже не соблюдая требований реального времени.

Тема 8. Таймер 2 микроконтроллера ADuC842

8.1. Общие сведения

Таймер 2 имеет целый ряд особенностей и дополнительных возможностей по сравнению с Таймером 0 и Таймером 1 в классических микроконтроллерах 8051. Таймер 2 ассоциируется с группой специальных регистров:

Таймер 2 (обозначаемый T/C 2) может работать в качестве 16-разрядного таймера, в режиме автоперезагрузки, в режиме генератора синхронизации при последовательном обмене данными, а также имеет дополнительный режим – режим захвата (capture mode).

Регистр управления T2CON имеет следующий формат:

Рисунок 8.1 – Формат регистра T2CON

Назначение битов этого регистра приведено ниже в таблице.

Таблица 8.1

Режим работы T/C 2 устанавливается сочетанием битов регистра T2CON, как это показано в таблице 8.2.

Функционирование схемы иллюстрирует временная диаграмма работы 8-разрядного преобразователя, представленная на рисунке 7.2.

Рисунок 7.2 – Преобразование в АЦП последовательного приближения

В начале цикла преобразования все выходы РПП принудительно устанавливаются в логический 0 за исключением старшего разряда. Это формирует на выходе ЦАП сигнал, значение которого равно «10000000». Если входное напряжение меньше половины входного диапазона АЦП, тогда выход компаратора примет значение логического 0. Это дает регистру последовательного приближения команду переключить свои выходы в состояние «01000000», что соответственно приведет к изменению выходного напряжения ЦАП, подаваемого на компаратор. Если при этом выход компаратора по-прежнему оставался бы в нуле, то выходы регистра переключились бы в состояние «00100000». Но на этом такте преобразования выходное напряжение ЦАП меньше, чем входное напряжение, и компаратор переключается в состояние логической 1. Это предписывает регистру последовательного приближения сохранить «1» во втором разряде и подать «1» на третий разряд. Описанный алгоритм работы затем вновь повторяется до последнего разряда.

7.2. Аналого-цифровой преобразователь микроконтроллера ADuC842

Микроконтроллер ADuC842 включает в свой состав блок АЦП, содержащий 9-канальный мультиплексор, встроенный источник опорного напряжения (ИОН), устройство выборки-хранения, схему калибровки и 12-разрядный АЦП последовательного приближения с однополярным питанием.

Мультиплексор служит для подключения одного из источников аналоговых сигналов (ADC0-ADC7) ко входу АЦП. Выбор источника сигнала для преобразования осуществляется посредством записи номера канала в соответствующие разряды регистра управления АЦП.

Преобразователь воспринимает входные аналоговые сигналы в диапазоне от 0 до +UREF. Может использоваться опорное напряжение U

REF, формируемое встроенным источником (ИОН), либо подаваемое от внешнего источника.

Режимы преобразования (однократный или циклический) могут быть установлены программно. Кроме того, преобразование может быть инициализировано внешним сигналом запуска на выводе CONVST. Для запуска повторяющегося процесса преобразования можно использовать сигнал Таймера

2.

Преобразователь можно установить в режим передачи данных по каналу прямого доступа к памяти (DMA). При этом блок повторяет циклы преобразования и посылает выборки во внешнюю память данных, минуя процессор.

Для управления АЦП используются три управляющих регистра ADCCON1, ADCCON2, ADCCON3, два регистра данных ADCDATAH и ADCDATAL, два регистра калибровочного коэффициента по усилению ADCGAINL и ADCGAINH, а также регистры калибровочного коэффициента по смещению нуля ADCOFSL и ADCOFSH.

Регистр ADCCON1 управляет запуском преобразования. Назначение разрядов регистра приведено в таблице 7.1.

Таблица 7.1. Регистр ADCCON1 управления АЦП

Запустить преобразование можно программно при помощи бита MD1, сигналом переполнения Таймера 2 и при помощи сигнала CONVST, который подается на вывод Р3.5. Дополнительно в этом регистре выбирается делитель для получения тактовой частоты преобразования СК (таблица 7.2) и время задержки для распространения сигнала AQ в тактах (таблица 7.3).

Таблица 7.2. Выбор тактовой частоты преобразования

Таблица 7.3. Выбор задержки сигнала

Регистр ADCCON2 предназначен для выбора источника сигнала, а также режима преобразования. Назначение разрядов регистра приведено в таблице 7.4.

Таблица 7.4. Регистр ADCCON2 управления АЦП

АЦП может выполнять однократные и циклические преобразования. Однократное преобразование выполняется при установленном бите SCONV (Single Conversion). По окончании преобразования устанавливается флаг прерывания ADCI. Время одного преобразования составляет 16 тактов частоты, поступающей на АЦП, плюс число тактов задержки (таблица 7.3).

Циклическое преобразование выполняется при установленном бите CCONV (Continuous Conversion). В этом режиме АЦП непрерывно преобразует входной аналоговый сигнал с частотой, установленной битами СК и AQ в регистре ADCCON1. Следует иметь в виду, что максимальная частота преобразования отводит управляющей программе на обслуживание одного преобразования всего 2 мкс (максимум 32 машинных цикла), включая время обслуживания прерывания. Поэтому АЦП может работать в режиме прямого доступа к памяти (DMA) , в котором результаты преобразования записываются во внешнюю память данных без участия процессора и обрабатываются позднее.

Таблица 7.5. Выбор источника аналогового сигнала

Регистр ADCCON3 используется для калибровки АЦП. Назначение разрядов регистра приведено в таблице 7.6.

Таблица 7.6. Регистр ADCCON3 управления АЦП

Микросхема поставляется потребителю откалиброванной. Это означает, что результат преобразования скорректирован для уменьшения влияния дрейфа (медленного изменения) постоянных токов в цепях АЦП.

Тем не менее, при эксплуатации устройства может понадобиться его калибровка для повышения точности измерений. Вовремя цикла калибровки устанавливается преобразование аналогового нуля или опорного напряжения с тем, чтобы результат преобразования тоже был равен нулю или опорному напряжению. Калибровка выполняется несколькими выборками. Количество выборок определяется битами AVGSx по таблице 7.7.

За один цикл выполняется калибровка либо смещения нуля, либо коэффициента усиления передаточной характеристики. Выбор типа калибровки выполняется битом TYPICAL. Сначала должна выполняться калибровка нуля при подаче на вход сигнала нуля. Затем выполняется калибровка усиления с подачей на вход сигнала опорного напряжения UREF. Калибровочные коэффициенты имеют разрядность 14 бит.

Таблица 7.7. Выбор числа выборок калибровки

Преобразование аналогового сигнала в цифровой осуществляется в диапазоне от 0 до UREF, которое составляет 2,5 В при использовании внутреннего ИОН. При этом точность измерения составляет UREF / 212=0,61 мВ. Значение преобразования можно вычислить, если умножить точность преобразования на результат преобразования. Так, если результат преобразования равен 964, измеряемое напряжение равно 0,588 В. Максимальное значение преобразования 4095 соответствует опорному напряжению.

После программирования блока АЦП с использованием регистров ADCCON1 – ACCON3 он начинает выполнять преобразования аналоговых входных сигналов и формировать 12-разрядные выходные коды в регистрах ADCDATAH(L). В старшие четыре разряда регистра ADCDATAH записывается номер канала. Формат слова результата показан на рисунке 7.3.

Рисунок 7.3 – Формат слова результата АЦП

7.3. Разметка внешней памяти данных в режиме прямого доступа к памяти

Режим прямого доступа к памяти обеспечивает реализацию максимального быстродействия АЦП. До включения режима DMA необходимо разметить внешнюю память, в которую будут записываться выборки. Разметка состоит в записи номеров каналов во внешнюю память. На рисунке 7.4 показана типовая разметка внешней памяти. После завершения разметки в регистры

Рисунок 7.4 – Разметка внешней памяти данных для режима DMA

DMAP, DMAH и DMAL заносится стартовый адрес DMA. В примере на рисунке 7.4 этот адрес равен h000000. Конец таблицы DMA указывается записью кода «1111» в поле номера канала. Теперь можно инициировать режим DMA установкой бита разрешения (ADCCON2.6, DMA).

Режим DMA включается только в том случае, если пользователь предварительно установил время преобразования и режим запуска в регистрах ADCCON1 и ADCCON2. В конце цикла DMA устанавливается бит прерывания АЦП (ADCCON2.7, ADCI), а внешняя память данных оказывается загруженной результатами, как показано на рисунке 7.5. Результаты разметки сохраняются.

Рисунок 7.5 – Внешняя память данных после цикла DMA

Во время цикла DMA процессор свободен и может выполнять команды, однако доступ процессора к портам Р2 и Р0 (которые используются контроллером DMA) в это время запрещен. Это означает, что если при выполнении программы встретится обращение к портам Р2 и Р0, данные с внешних выводов прочитаны не будут. Как только блок данных DMA будет записан во внешнюю память, инициируется прерывание и процедура обслуживания может обработать данные уже не соблюдая требований реального времени.

Тема 8. Таймер 2 микроконтроллера ADuC842

8.1. Общие сведения

Таймер 2 имеет целый ряд особенностей и дополнительных возможностей по сравнению с Таймером 0 и Таймером 1 в классических микроконтроллерах 8051. Таймер 2 ассоциируется с группой специальных регистров:

-

T2CON – регистр управления и контроля, является адресуемым побитово; -

RCAP2H – старший байт, содержимое которого используется при работе в режиме автоперезагрузки; -

RCAP2L – младший байт, содержимое которого используется при работе в режиме автоперезагрузки; -

TH2 – старший байт Таймера 2; -

TL2 – младший байт Таймера 2.

Таймер 2 (обозначаемый T/C 2) может работать в качестве 16-разрядного таймера, в режиме автоперезагрузки, в режиме генератора синхронизации при последовательном обмене данными, а также имеет дополнительный режим – режим захвата (capture mode).

Регистр управления T2CON имеет следующий формат:

Рисунок 8.1 – Формат регистра T2CON

Назначение битов этого регистра приведено ниже в таблице.

Таблица 8.1

| Имя бита | Номер разряда | Назначение бита |

| TF2 | 7 | Флаг переполнения. Устанавливается аппаратно, сбрасывается программно. Не устанавливается, если либо RCLK, либо TCLK установлены в «1». |

| EXF2 | 6 | Внешний флаг Таймера 2. Устанавливается аппаратно при защелкивании информации в регистрах захвата или при перезагрузке вследствие перехода 1 → 0 на выводе Р1.1 (T2EX) при EXEN2=1. Сбрасывается программно. |

| RCLK | 5 | Разрешение тактовых сигналов приема. Если установлен, Таймер 2 используется для тактирования приема в режимах 1 и 3. |

| TCLK | 4 | Разрешение тактовых сигналов передачи. Если установлен, Таймер 2 используется для тактирования передачи в режимах 1 и 3. |

| EXEN2 | 3 | Разрешение внешнего сигнала T2EX. Устанавливается для разрешения захвата или перезагрузки вследствие перехода 1 → 0 на выводе Р1.1 (T2EX). |

| TR2 | 2 | Бит запуска Таймера 2. |

| CNT2 | 1 | Выбор режима работы. Если установлен, Таймер 2 работает как счетчик сигналов на выводе Т2. Если сброшен - работает как таймер. |

| CAP2 | 0 | Выбор режима захвата/перезагрузки. Если установлен, разрешен захват по переходу 1 → 0 на выводе Р1.1 при EXEN2=1. Если сброшен, разрешается перезагрузка по переполнению или переходу 1 → 0 на выводе Р1.1 при EXEN2=1. Бит игнорируется, если либо RCLK, либо TCLK установлены в «1». |

Режим работы T/C 2 устанавливается сочетанием битов регистра T2CON, как это показано в таблице 8.2.