Файл: Проектирование многоразрядного десятичного сумматора комбинационного типа.doc

Добавлен: 07.11.2023

Просмотров: 62

Скачиваний: 5

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

Разработка схемы для определения знака суммы.

Согласно правилам сложения в обратном коде, знаковые разряды участвуют в операции сложения наравне с остальными разрядами. При этом учитывается перенос в знаковый разряд и перенос из знакового разряда. Поэтому для получения знака результата можно использовать одноразрядный двоичный сумматор.

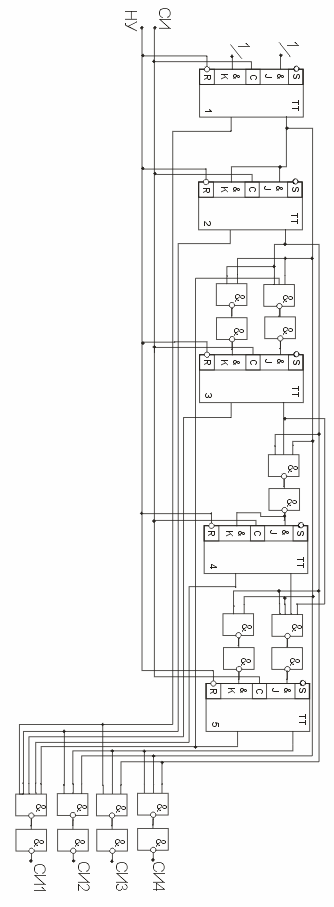

Разработка функциональной схемы многоразрядного десятичного сумматора.

На вход сумматора поступают: A=a0a1a2a3 и B=b0b1b2b3, где ai=8421 и bi=8421.

Результат от сложения: C=c1c2c3c4, где ci=8421.

Функциональная схема 3-х разрядного десятичного сумматора.

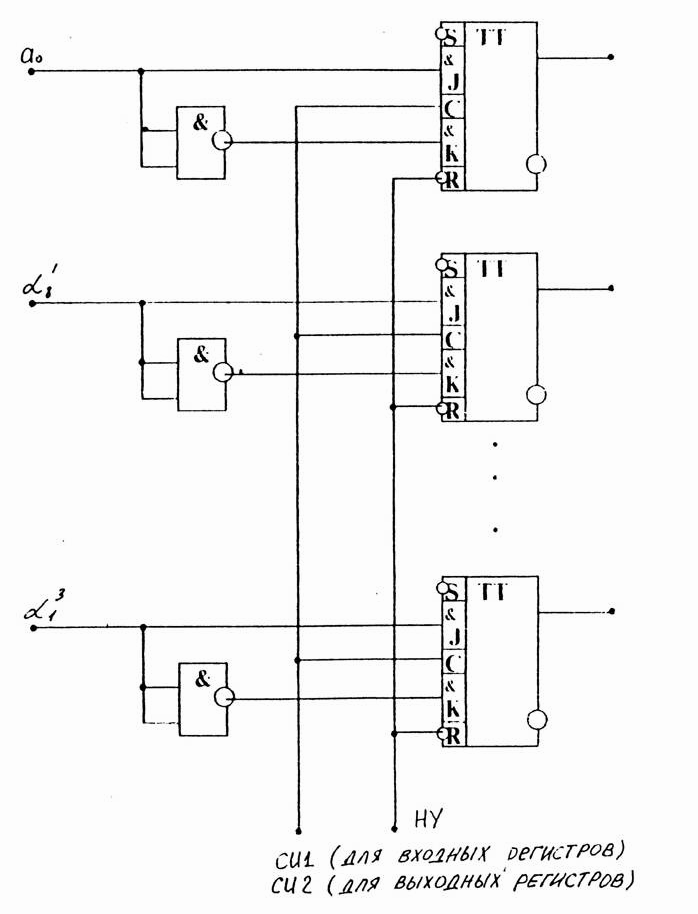

Разработка входных и выходных регистров хра¬ния числовой информации, участвующей в операции сложения.

Регистры входов и выхода имеют одинаковую структуру и строятся на двухтактных синхронных J-K триггерах. Каждый регистр содержит 13 триггеров (12 значащих и 1 знаковый).

На вход J триггера подается информационный бит, на вход K – его инверсия.

На синхровходы С подается сигнал с распределителя сигналов, на инверсные входы R подается сигнал начальной установки, переводящий триггеры в нулевое состояние

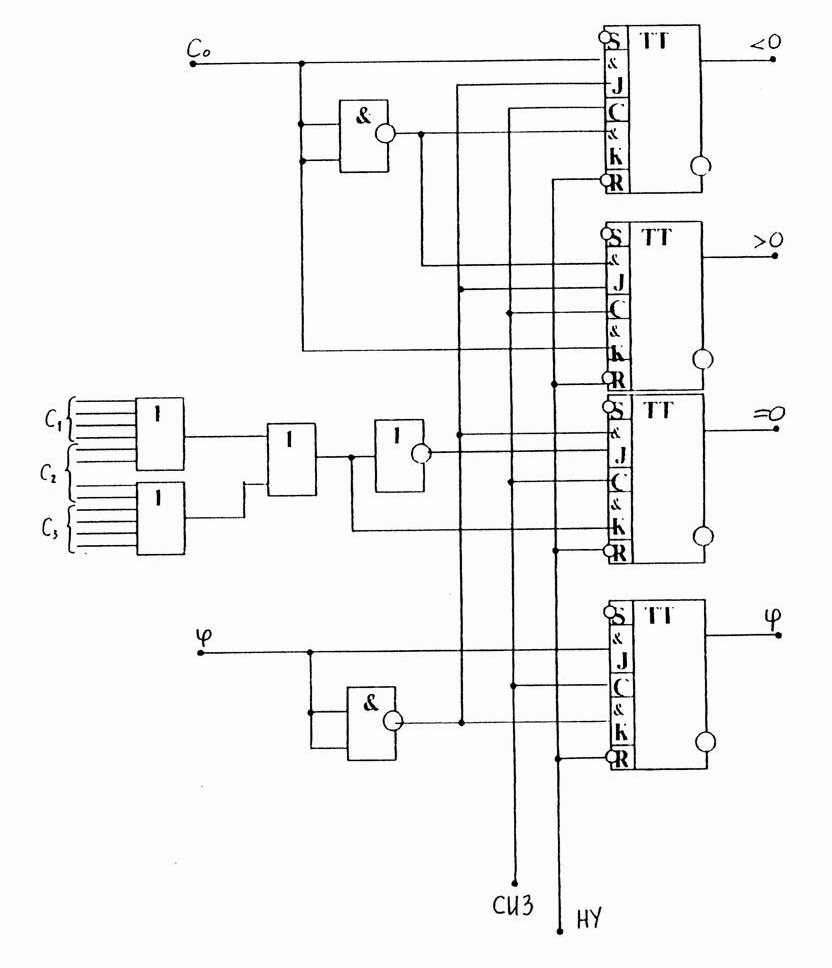

Разработка регистра признаков результата.

Регистр признаков хранит информацию о результате работы устройства. Регистр состоит из 4 триггеров. Первый дает 1, если результат отрицательный, второй положительный, третий равен нулю, четвертый произошло переполнение (при этом первые три триггера блокируются). Входными сигналами для первых двух триггеров является знак результата. Для триггера равенства результата нулю необходимый входной сигнал получается на комбинационной схеме, которая вырабатывает сигнал 1, когда все значащие разряды (двоичные) результата равны нулю. Входным сигналом четвертого триггера является сигнал с выхода схемы переполнения.

Для блокировки первых трех триггеров в случае переполнения на входы J этих триггеров следует также подать инверсию сигнала со схемы, фиксирующей переполнение. На все четыре триггера на синхровходы С подается сигнал СИ 3 от распределителя сигналов. На инверсные входы R подается сигнал НУ для перевода триггеров в начале выполнения операции в нулевое состояние.

Расчет временных параметров устройства управления.

Для правильного функционирования устройства ¬обходимо устройство, которое будет синхронизировать работу сумматора и регистров, а также осуществлять остановку после получения результата.

Это устройство, называемое распределителем сигналов, вырабатывает 4 синхроимпульса с различными временными задержками между ними. Первый импульс позволит записать два операнда во входные регистры. Одновременно нач¬т работу сумматор. Второй импульс позволит записать результат в выходной регистр, третий – получить в регистре признаков признаки результата. Четвертый импульс остановит процесс вычислений.

Распределитель сигналов имеет 4 выхода (по числу синхросигналов различного назначения) и один вход, на который подаются импульсы с тактового ге¬ратора. Ге¬ратор вырабатывает импульсы с частотой 2нс. и скважностью 1, распределитель должен выделить из этой последовательности 4 сигнала с определенной временной задержкой между ними. Величина задержки характеризуется време¬м работы схем, входящих в состав сумматора:

| Одноразрядный двоичный сумматор цепь P | 2 нс. |

| Одноразрядный двоичный сумматор цепь S | 3 нс. |

| Одноразрядный десятичный сумматор выход P | 13 нс. |

| Одноразрядный десятичный сумматор выход S | 19 нс. |

| Преобразователь | 3 нс. |

При прохождении сигнала через трехразрядный десятичный сумматор самой длинной цепью будет: прохождение операндов через входные преобразователи, перенос во всех разрядах включая знаковый и через преобразователи поступление результата на выход устройства (3+13*3 + 2 + 19 + 3 = 66 нс.). Задержка между первыми двумя синхроимпульсами должна быть кратна 4 и больше 66, следовательно, T1=68нс. Задержка на самой длинной цепи регистра признаков равна 3нс., поэтому, временной интервал между вторым и третьим импульсами T2=4нс.

Итак, распределитель сигналов является ге¬ратором следующих четырехразрядных двоичных чисел: 0001, 0000, … (16 раз) … , 0000, 0010, 0100, 1000.и будет проектироваться на основе счетчика с пересчетом на 20.

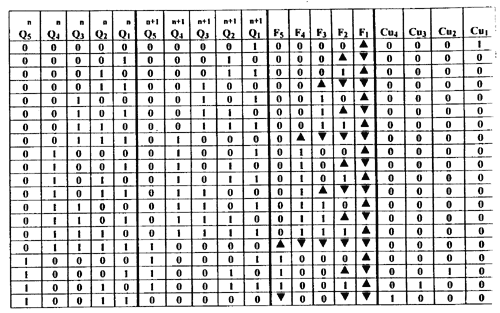

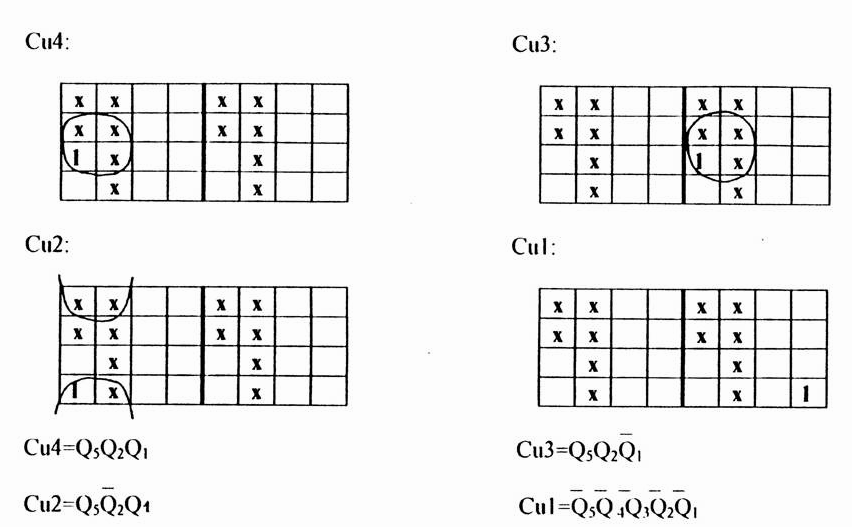

Составим таблицу переходов:

Такт n Такт n+1 Словарная функция Выходы распределителя

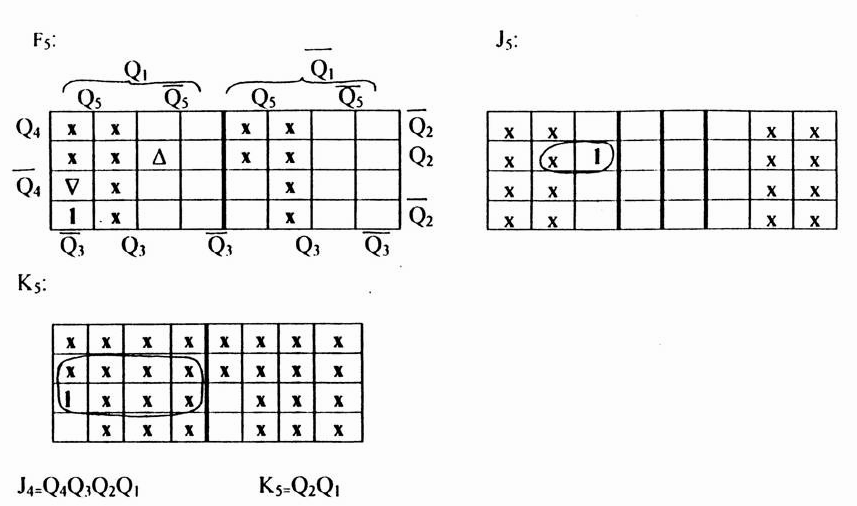

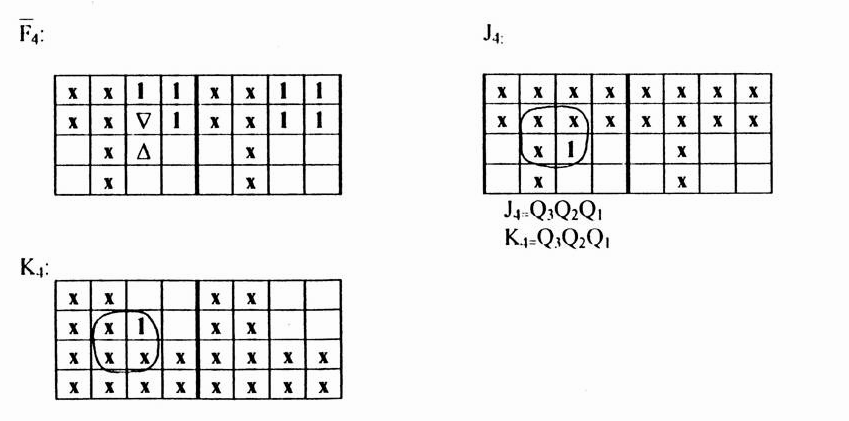

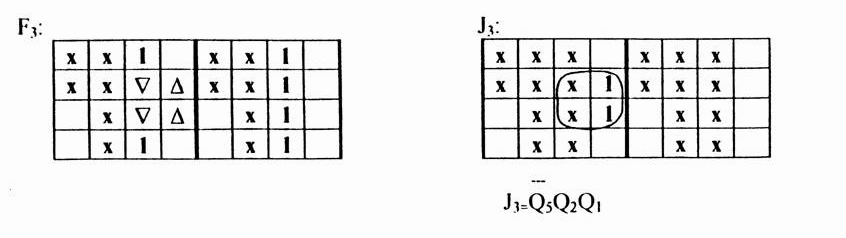

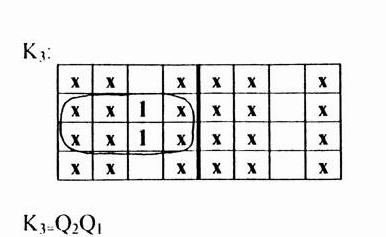

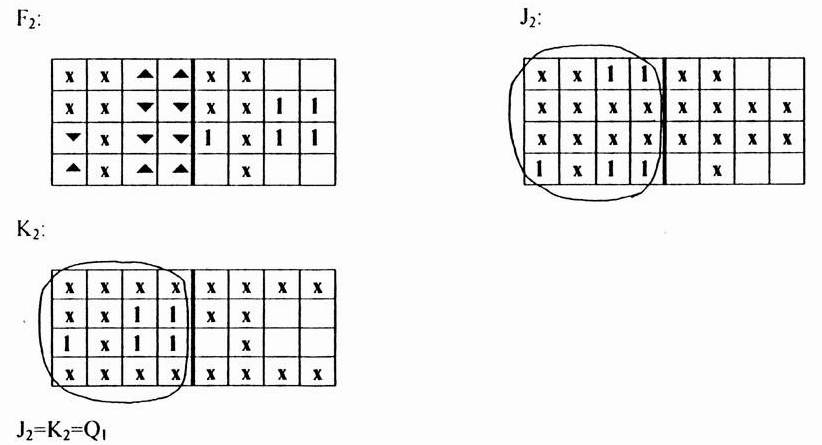

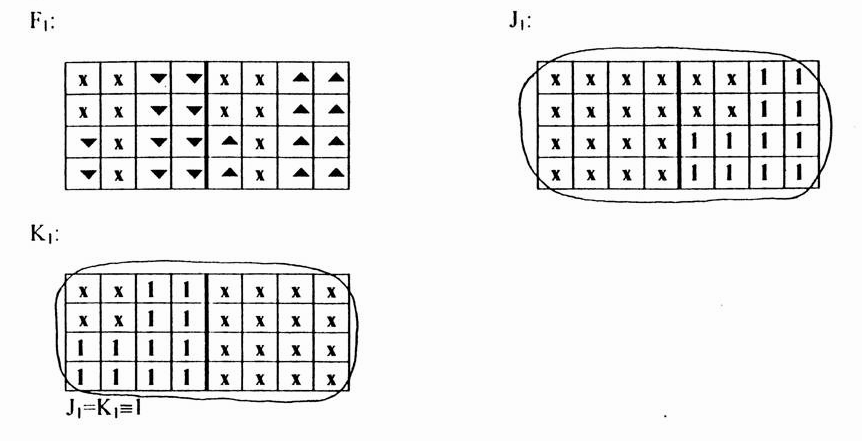

Теперь нанесем на диаграммы значения переключательных функций Сu1, Сu2, СuЗ и Сu4 и получим логические уравнения для проектирования комбинационной схемы

По всем полученным логическим уравнениям можно построить функциональную схему распределителя сигналов:

По всем полученным логическим уравнениям можно построить функциональную схему распределителя сигналов:

Общая структура схемы многоразрядного десятичного сумматора комбинационного типа с устройством управления.