ВУЗ: Казахская Национальная Академия Искусств им. Т. Жургенова

Категория: Учебное пособие

Дисциплина: Не указана

Добавлен: 03.02.2019

Просмотров: 17368

Скачиваний: 18

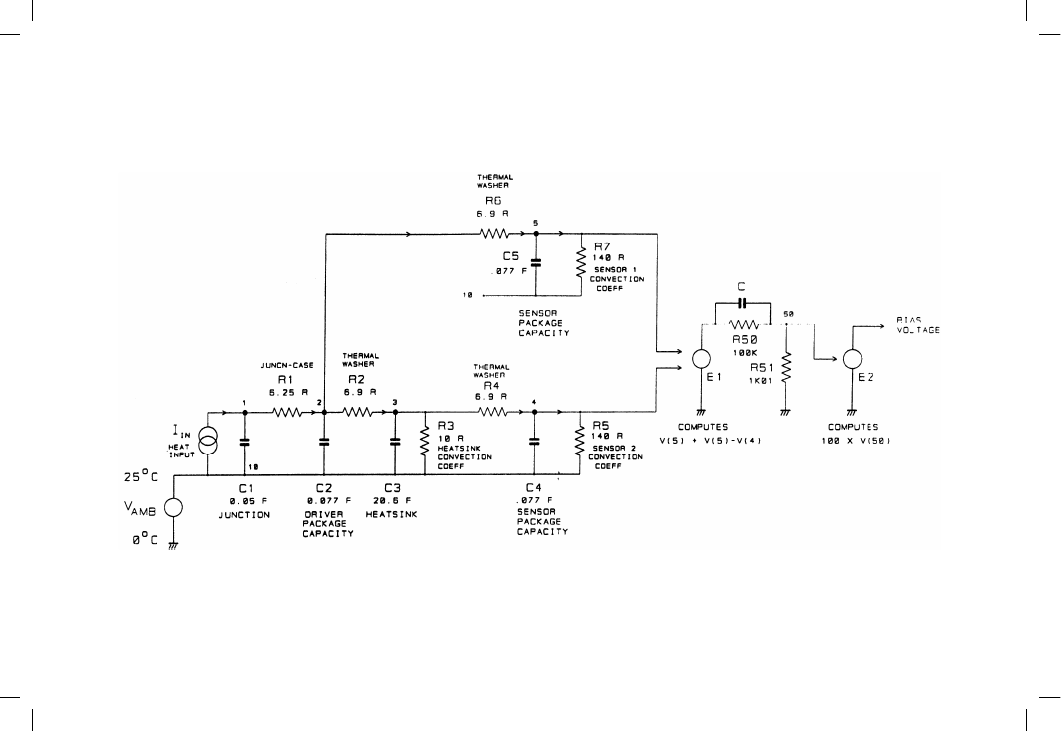

Figure 12.24

The conceptual circuit

of a junction-estimator

with dynamics. C gives

higher gain for fast

thermal transients and

greatly reduces the

effects of delay

Audio Power Amplifier Design Handbook

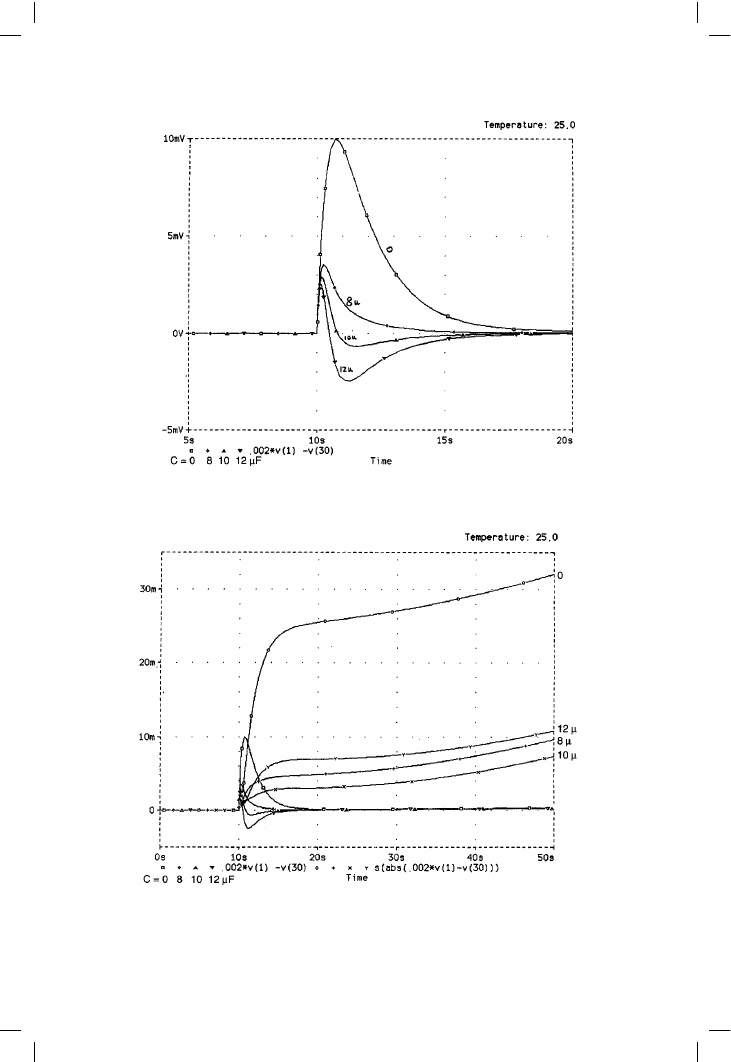

Figure 12.25

The initial transient errors for different values of C. Too high a value causes undershoot

Figure 12.26

The IAE for different values of C. 10 µF is clearly best for minimum integrated error (IAE = 7.3 mV-sec) but

even a rough value is a great improvement

356

Thermal compensation and thermal dynamics

With C set to 10 µF, the transient error falls within a +/–1 mV window

after only 0.6 seconds, which is more than twenty times faster than the

first improved CFP version (sensor put on driver) and gives a nicely

reduced IAE of 7.3 mV-sec at 50 seconds. The real-life circuitry to do this

has not been designed in detail, but presents no obvious difficulties. The

result should be the most accurately bias-compensated Class-B amplifier

ever conceived.

Conclusion

Some of the results of these simulations and tests were rather unex-

pected. I thought that the CFP would show relatively smaller bias errors

than the EF, but it is the EF that stays within its much wider tolerance

bands, with either heatsink or TO3-top mounted sensors. The thermal-

gain effect in the EF stage seems to be the root cause of this, and this in

turn is a consequence of the near-constant driver dissipation in the EF

configuration.

However, the cumulative bias errors of the EF stage can only be reduced to

a certain extent, as the system is never free from the influence of the main

heatsink with its substantial thermal inertia. In contrast the CFP stage gives

much more freedom for sensor placement and gives scope for more

sophisticated approaches that reduce the errors considerably.

Hopefully it is clear that it is no longer necessary to accept Vbe-multiplier

on the heatsink as the only option for the crucial task of Vbias

compensation. The alternatives presented promise greatly superior com-

pensation accuracy.

Variable-tempco bias generators

The standard Vbe-multiplier bias generator has a temperature coefficient

that is fixed by the multiplication factor used, and so ultimately by the value

of Vbias required. At many points in this chapter it has been assumed that

it is possible to make a bias generator with an arbitrary temperature

coefficient. This section shows how to do it.

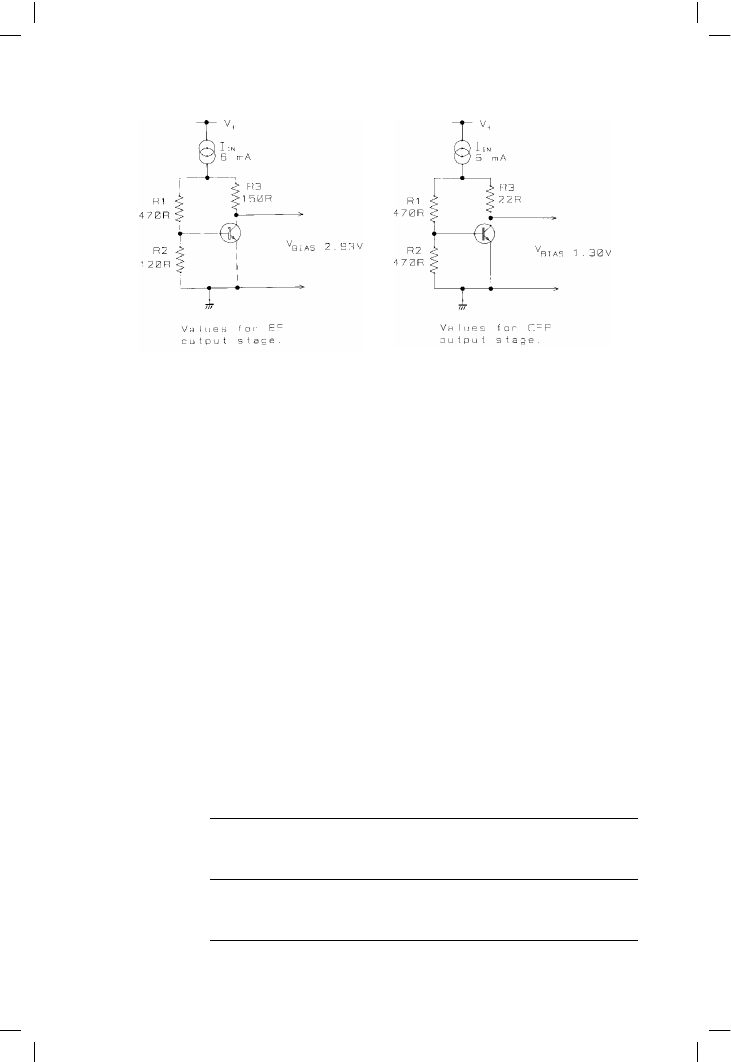

Figure 12.27 shows two versions of the usual Vbe-multiplier bias generator.

Here the lower rails are shown as grounded to simplify the results. The first

version in Figure 12.27a is designed for an EF (Emitter-Follower) output

stage, where the voltage Vbias to be generated is (4

× Vbe) + Vq, which

totals +2.93 V. Recall that Vq is the small quiescent voltage across the

emitter-resistors Re; it is this quantity we are aiming to keep constant, rather

than the quiescent current, as is usually assumed. The optimal Vq for an EF

stage is in the region of 50 mV.

357

Audio Power Amplifier Design Handbook

The second bias generator in Figure 12.27b is intended for a CFP

(Complementary-Feedback-Pair) output stage, for which the required Vbias

is less at (2

× Vbe) + Vq, or approx 1.30 V in total. Note that the optimal Vq

is also much smaller for the CFP type of output stage, being about 5 mV.

It is assumed that Vbias is trimmed by varying R2, which will in practice be

a preset with a series end-stop resistor to limit the maximum Vbias setting.

It is important that this is the case, because a preset normally fails by the

wiper becoming disconnected, and if it is in the R2 position the bias will

default to minimum. In the R1 position an open-circuit preset will give

maximum bias, which may blow fuses or damage the output stage. The

adjustment range provided should be no greater than that required to take

up production tolerances; it is, however, hard to predict just how big that

will be, so the range is normally made wide for pre-production

manufacture, and then tightened in the light of experience.

The EF version of the bias generator has a higher Vbias, so there is a larger

Vbe-multiplication factor to generate it. This is reflected in the higher

temperature coefficient (hereafter shortened to ‘tempco’). See Table 12.4.

358

(a)

(b)

Figure 12.27

The classical Vbe-multiplier bias generator. Two versions are shown: for biasing EF (a) and (b) CFP output

stages. The EF requires more than twice the bias voltage for optimal crossover performance

Table 12.4

Vbias

volts

R1

!

R2

!

R3

!

Tempco

mV/°C

EF

2.93

120R

470R

22R

–9.3

CFP

1.30

470R

470R

150R

–3.6

Thermal compensation and thermal dynamics

Creating a higher tempco

A higher (i.e. more negative) tempco than normal may be useful to

compensate for the inability to sense the actual output junction tem-

peratures. Often the thermal losses to the temperature sensor are the major

source of steady-state Vbias error, and to reduce this a tempco is required

that is larger than the standard value given by: ‘Vbe-multiplication factor

times –2 mV/°C’. Many approaches are possible, but the problem is

complicated because in the CFP case the bias generator has to work within

two rails only 1.3 V apart. Additional circuitry outside this voltage band can

be accommodated by bootstrapping, as in the Trimodal amplifier biasing

system in Chapter 9, but this does add to the component count.

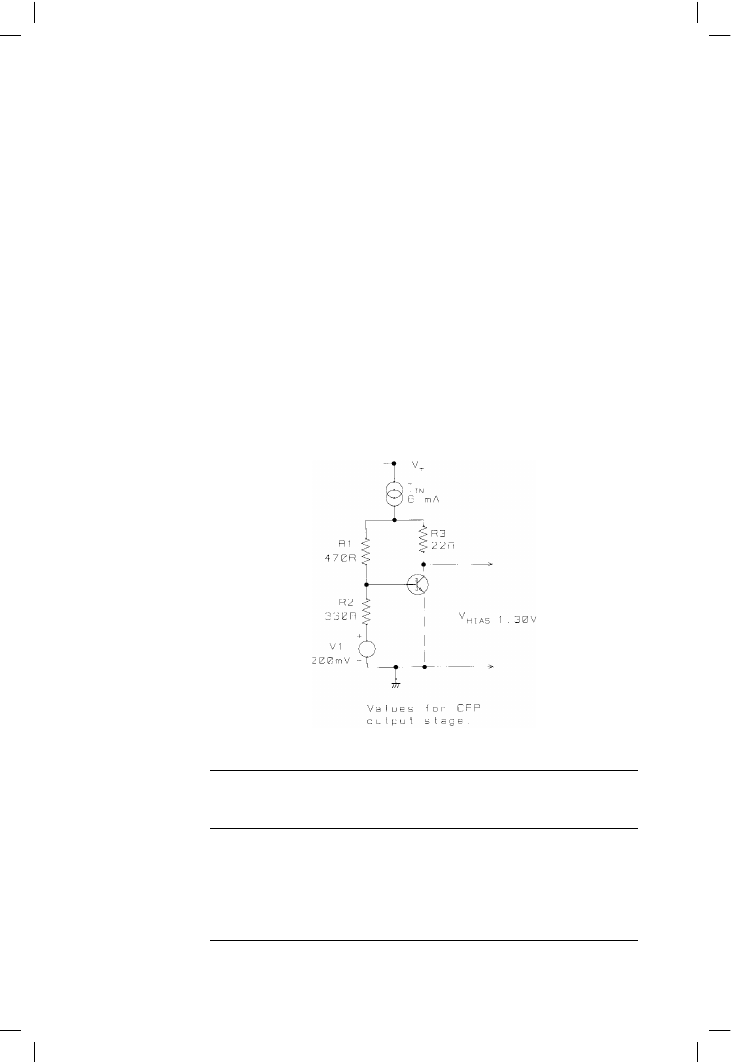

A simple new idea is shown in Figure 12.28. The aim is to increase the

multiplication factor (and hence the negative tempco) required to give the

same Vbias. The diagram shows a voltage source V1 inserted in the R2 arm.

To keep Vbias the same, R2 is reduced. Since the multiplication factor

(R1 + R2)/R2 is increased, the tempco is similarly increased. In Table 12.5,

359

Figure 12.28

Principle of a Vbe

multiplier with

increased tempco.

Adding voltage source

V1 means the voltage-

multiplication factor

must be increased to

get the same Vbias.

The tempco is therefore

also increased, here to

–4.4 mV/°C

Table 12.5

V1

mV

Vbias

V

R2

!

Tempco

mV/C

0

1.287

470

–3.6

100

1.304

390

–4.0

200

1.287

330

–4.4

300

1.286

260

–5.0

400

1.285

190

–6.9