Файл: MatLab ортасында сандарды онды жне екілік санау жйесіне айналдыру алгоритмін жзеге асыру Жмысты масаты.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.11.2023

Просмотров: 262

Скачиваний: 2

ВНИМАНИЕ! Если данный файл нарушает Ваши авторские права, то обязательно сообщите нам.

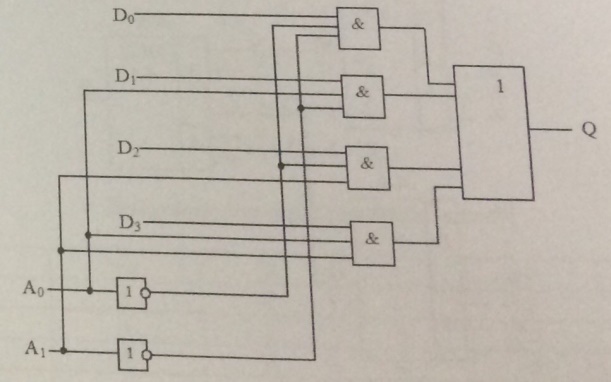

Аналитикалық теңдеудің негізінде мультиплексордың функционалды сұлбасы (7.2-сурет) алынады.

7.2-сурет. Мультиплексордың функционалды сұлбасы

Мультиплексор шығыстары кірісті НЕМЕСЕ элементінің көмегімен дизъюнктивті бірікккен n конъюнктордан тұрады (7.2-сурет). Жоғарыда айтып кеткендей, мультиплексордың кірістері екі түрде болады: ақпараттық және баскарушы кірістер. Сұлбадағы D0, D1, D2, D3 - ақпараттық кіріс, ал А0, А1 - басқарушы кіріс болып табылады.

Коньюнкцияның барлық элементтерінің бір кірісіне ақпараттық сигналдар беріледі, ал басқа кірістері n кірісті дешифратордың сәйкес шығыстары мен қосылады.

Функционалды сұлбадан мультиплексор шығыс санына сәйкес дешифраторға және әрқайсысы екі немесе үш кірісі бар коньюнкция элементтеріне және D0, D1, D2, D3 мультиплексордың кірістер санына тең дизъюнкция элементіне ие екенін көруге болады.Дешифратордың шыгыс саны мультиплексорлың ақтараттық кірістер санымен анықталады.

Мультиплексорлар есептеу техникасында цифрлық сигналдар коммутаторы ретінде кеңінен қолданылады, Олар компьютерлерде және микропроцессорлы контроллеры динамикалық оперативті есте сактау құрылғыларының адрестік кірістерін коммутациялау үшін шиналардың бірігу немесе тармақталу түйіндерінде қолданылады.

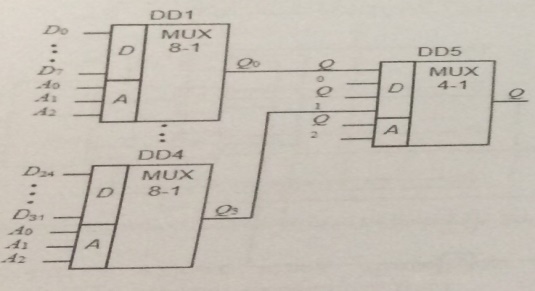

Мультиплексордың разрядын арттыру үшін бірнеше мультиплексорды жинақтау қажет.

7.3.- сурет. 32-1 разрядты мультиплексор

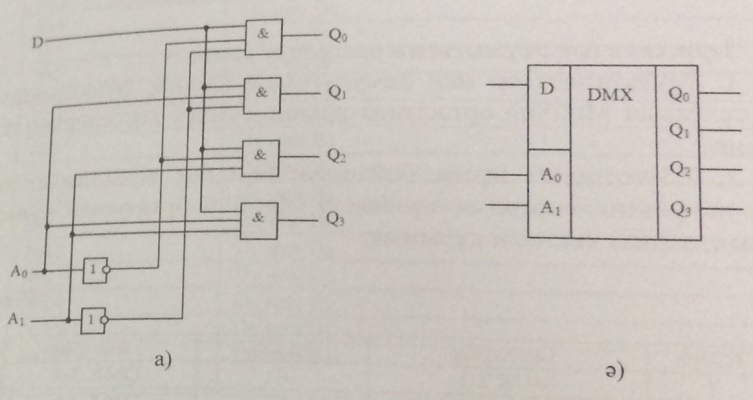

Демультиплексор. Маліметтерді бір кіріс каналынан бірнеше қабылдау каналаның біреуіне береді. Оның функционалдық схемасы (a) және шартты-графикалық белгіленуі (ә) 7.4-суретте көрсетілген.

7.4-сурет. Демультиплексордың функционалды сұлбасы (а) және оның шартты – графикалық белгіленуі

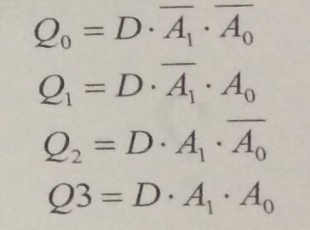

Суреттен көріп отырғанымыздай, демультиплексордың кірісіне тек бір ғана ақпаратты сигнал беріледі. Басқарушы кірістердің кодына сайкес келетін шығыстың біреуіне ғана ақпаратты сигнал жеткізіледі. Демультиплексордың аналитикалық теңдеуі төменде келтірілген.

7. 1-кесте

Демультиплексордың ақиқат кестеcі

| А1 | А0 | Q3 | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 0 | 0 | D |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 1 | 1 | D | 0 | 0 | 0 |

7.2.- кестеде келтірілген демультиплексордың ақиқат кестесі бойынша демультиплексордың жұмысын түсіндіруге болады.Бір канал арқылы ақпаратты сигнал ( D ) беріледі, ал басқарушы каналдары ( А1, А0) арқылы шығыс каналдардың ( Q3, Q2, Q1, Q0 ) қайсысына ақпаратты сигнал берілетіні анықталынады.

Зертханалық жұмыстың орындалу реті:

-

Мультиплексор мен демультиплексордың функционалды сұлбасын MultiSim ортасында жинап, ақиқат кестелерін тексеріңіз. -

7.3.- кестедегі нұсқа бойынша берілген мультиплексор мен демультиплексордың сұлбасын MultiSim ортасында құрастырып, ақиқат кестесін құрыңыз;

7.3- кесте

| Нұсқа | Тапсырма | Нұсқа | Тапсырма |

| 1 | MUX 2 – 1 | 4 | DMX 2 -4 |

| 2 | MUX 4 - 1 | 5 | DMX 3 – 8 |

| 3 | MUX 8 -1 | 6 | DMX 4- 16 |

| | | | |

-

7.5 – суретте көрсетілген сұлбадағы абоненттер арасындағы байланысты орнату үшін сұлбаға қойылатын шарттарды атаңыз және сұлбасын құрыңыз ( 7.4 – кестені қолданыңыз).

7.5 – сурет

7.4 – кесте

Бақылау сұрақтары:

1. Мультиплексор мен демультиплексорға анықтама беріңіз.

2. Комбинациялық сұлбалар дегеніміз не?

3. Мультиплексордың ақиқат кестесін қолдана отырып, аналитикалық теңдеуін жазыңыз.

4. Демультиплексордың көмегімен параллельді кодты қайталаушы кодқа түрлендіру дегеніміз не?

5. Мультиплексордың көмегімен параллельді кодты қайталаушы кодқатүрлендіру калай жүзеге асады?

№8 Зертханалық жұмыс

Транзисторлы-транзисторлы логика және диодты-

транзисторлы логика микроссұлбаларының негізінде

логикалық элементтердің сұлбаларын зерттеу

Жұмыстың мақсаты: ТТЛ жане ДТЛ микросұлбаларының технологияларын жане микросұлбалардың негізінде логикалық элементтердің жұмыс істеу принциптерін зерттеу

Қысқаша теориялық кіріспе:

Логикалық элементтерді немесе логикалық микросұлбаларды жасауда бірнеше технологиялар қолданылады, технологиялардың бірнеше сериялары бар, олар элементтердің жнынтығына, қорек көзіне, қолданылатын қуатына, динамикалық параметрлеріне және т. б. көрсеткіштерге байланысты ерекшеленеді. Жиі қолданылатын ИМС сериялары: транзисторлы-транзисторлы логика (ТТЛ), эмиттерлі байланыс логикасы (ЭБЛ), кешенді металл-оксидті жартылай өткізгіш (КМОЖ), диодты-транзисторлы логика (ДТЛ).

ТТЛ сұлбасында "2 ЖӘНЕ" логикалық элементін іске асыру үшін параллельді жалғанған диодтардың орнына көпэмиттерлі транзистор қолданылады. Логикалық элементтің жұмыс істеу физикасы диодты логикалық элементінің жұмыс істеу принципінен айырмашылығы жоқ. Логикалық элементтің екі кірісінде де (транзистордың эмиттерлерінде) жоғарғы потенциал болған жағдайда, көпэмиттерлі транзистордың шығысындағы потенциал жоғары болады. ТТЛ микросұлбасының негізгі логикалық элементінің құрылымдылық сұлбасы 8.1-суретте келтірілген.

8.1 – сурет. ТТЛ микросұлбасының негізгі логикалық элементінің құрылымдық сұлбасы

Көбейтетін күшейткіш диодты-транзисторлы элемент сияқты логикалық элемент сұлбасының шығысында сигналды инверттейді. Осындай принцип бойынша ТТЛ микросұлбаларының негізгі логикалық элементтерінің 155, 131 және 531 сериялары жасалған. "ЖӘНЕ-ЕМЕС" логикалык микросұлбаларында «ЛА» деген жазу болады. Мысалы, К531ЛАЗ сұлбасының бір корпусында төрт "2ЖӘНЕ-ЕМЕС" логикалық элементі бар. Осы сұлбаның ақиқат кестесі 8.1-кестеде келгірілген, ал оның шартты графикалық белгіленуі 8.2-суретте көрсетілген.

8.2-сурет.«ЖӘНЕ-ЕМЕС" логикалық элементінің шақты графикалық белгіленуі

8. 1-кесте

"2ЖӘНЕ-ЕМЕС" логикалық элементінін ақиқат кестесі

| x1 | x2 | F |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Негізгі логикалық элементтің негізінде инвертор сұлбасы кұрылады. Бұл жағдайда сұлбаның кірісіне тек бір ғана диод қажет. ТТЛ негізіндегі инвертор сұлбасы 8.3-суретте көрсетілген.

8.3-сурет. ТТЛ негізінде құрастырылған инвертордың кұрылымдық сұлбасы

Бірнеше "ЖӘНЕ" логикалық элементін «НЕМЕСЕ» элементі арқылы қосу қажет болған жағдайда (немесе «НЕМЕСЕ» логикалык элементін жүзеге асыру кезінде), VT2 транзисторлары "а" және "б" нүктелерінде параллель жалғанады (8.4-сурет) және тек бір ғана шығыс каскады қолданылады. "2 ЖӘНЕ-НЕМЕCE-EMEC» логикалық элементінің құрылымдылық сұлбасы 8.4-суретте көрсетілген.

8.4-сурет. "2ЖӘНЕ-2 НЕМЕСЕ-ЕМЕС" логикалық элементінің

кұрылымдылық сұлбасы

Логикалық элементтерді ақиқат кестесі бойынша ЖДНФ әдісі арқылы алынған сандық микро сұлбаларды жүзеге асыру кезінде жоғарыда айтылған қосылу сұлбалары кеңінен қолданылады. "2 ЖӘНЕ-2НЕМЕСЕ" логикалық элементінің шартты графикалық белгіленуі 8.5-суретте көрсетілген.

8.5-сурет. "2ЖӘНЕ-2HEMECE" логикалық элементінің шартты

графикалық белгіленуі

Заманауи ТТЛ және ДТЛ сұлбаларында бірдей шығыс күшейткіштер қолданылатындықтан, онда осы сұлбалардың да шығысындағы сигналдардың деңгейі бірдей болады.

Қазіргі кезде ТТЛ микросұлбасынын екі түрі қолданылады: корек кезі бес Және үш вольтты болатын сұлбалар, бірақ осы микро сұлбаларды шығысында микросұлбаның қорек көзіне тәуелсіз "0" және "1" логикалық деңгейі бірдій болып табылады. Сандық ТТЛ микросұлбасы шығысының рұқсат етілген кернеу деңгейі 8.6-суретте көрсетілген.

8.6-сурет. Сандық ТТЛ микросулбаларының шығысынданы сигналдардың

логика деңгейі

Сандық микросұлбаның шығысына караганда кірісіндегі кернеу үлкен шектерде жұмыс істеуге рұқсат ететіні жайлы жоғарыда айтып кеткен болатынбыз. ТТЛ микросұлбанары үшін нөл және бірлік логика деңгейінің шекарасы 8.7-суретте келтірілген.

8.7-сурет. Сандық ТТЛ микросұлбаның шығыс сигналының.

логикалық деңгейі

Логикалық микросұлбаларды алу кезінде диодтарда қолданылады. Диодтын көмегімен алынған логикалық элементтер өте қарапайым болып келеді. Диодты логиканың негізгі логикалық элементінің сұлбасы 8.8-суретте көрсетілген.

8.8-сурет. Диодтың негізіндегі "2ЖӘНЕ" негізгі логикалық

элементтің құрылымдылық сұлбасы

Диодтағы негізгі логикалық элементтердің сұлбасындағы кез келген кірісіне нөлдік потенциал (немесе екі кірісіне де бірдей) берілетін болса, онда R1 резистор арқылы ток жүретін болады және оның кедергісіне кернеу түседі. Нәтижесінде микросұлбаның екі кірісіне де бірлік потенциал берген жағдайда ғана негізгі логикалық элемент сұлбасының шығысында бірлік потенциал болады. Яғни келтірілген сұлба "2ЖӘНЕ " элементінің жұмысын атқарады.

«ЖӘНЕ» логикалық элементінің кірістерінің саны диодтардың санына байланысты болады. Егер екі диод қолданылса, онда " 2ЖӘНЕ" логикалық элементі болады, егер үш диод болса,онда "3ЖӘНЕ" логикалық элементі болады және т. с. с. Микросұлбаларда орташа ceriз кірісті «ЖӘНЕ» логикалық элементі бар.

Келтірілген «ЖӘНЕ» логикалық элементінің шығысында логикалық деңгей бойынша ығысу секілді кемшіліктер болады.Сұлбаның шығысындағы нелдік кернеу мен бірлік кернеу кіріс деңгейінен 0,7 В-қа жоғары. Бұл диодтардын кірісіне түсетін кернеудің азаюынан шығады. Диодты логикалық элементті 8.9-суретте корсетілген сұлба бойынша кұрау аркылы аталған кемшілік жойылады.

8.9-сурет. Диод негізіндегі жетілдірілген "2ЖӘНЕ" логикалық