Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 954

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

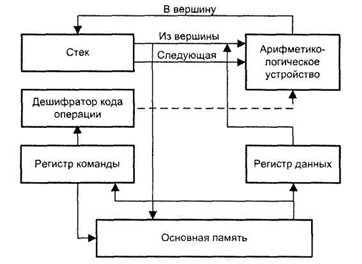

Основные узлы и информационные тракты одного из возможных вариантов микропроцессора на основе стековой архитектуры показаны на рис. 53.

Рисунок 53 – Архитектура микропроцессора на базе стека

Рисунок 53 – Архитектура микропроцессора на базе стекаИнформация может быть занесена в вершину стека из памяти или из АЛУ. Для записи в стек содержимого ячейки памяти с адресом x выполняется команда pushх, по которой информация считывается из ячейки памяти, заносится в регистр данных, а затем проталкивается в стек. Результат операции из АЛУ заносится в вершину стека автоматически. Сохранение содержимого вершины стека в ячейке памяти с адресом х производится командой popх. По этой команде содержимое верхней ячейки стека подается на шину, с которой и производится запись в ячейку х, после чего вся находящаяся в стеке информация проталкивается на одну позицию вверх.

Для выполнения арифметической или логической операции на вход АЛУ подается информация, считанная из двух верхних ячеек стека (при этом содержимое стека

продвигается на две позиции вверх, т.е. операнды из стека удаляются). Результат операции заталкивается в вершину стека. Возможен вариант, когда результат сразу же переписывается в память с помощью автоматически выполняемой операции pop x.

Верхние ячейки стековой памяти, где хранятся операнды и куда заносится результат операции, как правило, делаются более быстродействующими и размещаются в процессоре, в то время как остальная часть стека может располагаться в основной памяти.

К достоинствам стековой архитектуры следует отнести возможность предельного сокращения адресной части команд, поскольку все операции производятся через вершину стека, т. е. адреса операндов и результата в командах арифметической и логической обработки информации указывать не нужно. Поэтому код программы получается компактным, что экономит память. Достаточно просто реализуется декодирование команд, что способствуют повышению производительности микропроцессора. Однако при такой структуре команд возникают осложнения с построением команд передачи управления и работы с портами ввода/вывода.

Кроме того, стековая архитектура по определению не предполагает произвольного доступа к памяти, из-за

чего компилятору

трудно создать эффективный программный код, хотя создание самих компиляторов упрощается. Поэтому организация вычислений с использованием стековой памяти нашла применение только в специализированных микропроцессорах

36.Классификация команд микропроцессоров.

Несмотря на различие в системах команд разных МП, некоторые основные типы команд могут быть найдены в любом из них. К основным типам команд МП относятся следующие:

команды пересылки данных;

команды арифметической и логической обработки;

команды ввода/вывода;

команды управления микропроцессором;

команды передачи управления.

Командыпересылкиданных. Это наиболее распространенный тип машинных команд. Команды этого типа обеспечивают передачу информации между процессором и ОП, внутри процессора и между ячейками памяти.

Командыарифметическойилогическойобработки. В данную группу входят команды, обеспечивающие арифметическую и логическую обработку информации в различных формах ее представления. Для каждой формы представления чисел обычно предусматривается некоторый стандартный набор операций.

К стандартному набору операций над целыми числами, представленными в форме с фиксированной запятой, относятся:

двухместные арифметические операции (операции с двумя операндами): сложение, вычитание, умножение и деление;

одноместные арифметические операции (операции с одним операндом): вычисление абсолютного значения (модуля) операнда, изменение знака

операнда;

сложение с учетом переноса, вычитание с учетом заема, увеличение значения операнда на единицу (инкремент), уменьшение значения операнда на единицу (декремент);

операции сравнения, обеспечивающие сравнение двух целых чисел и выработку признаков, характеризующих соотношение между сопоставляемыми величинами: =, <>, >, <, <=, >=.

Для работы с числами, представленными в форме с плавающей запятой, обычно предусматриваются следующие операции:

основные арифметические операции: сложение, вычитание, умножение и деление;

операции сравнения, обеспечивающие сравнение двух вещественных чисел с выработкой признаков: =, <>, >, <, <=, >=;

операции преобразования: формы представления (между фиксированной и плавающей запятой), формата представления (с одинарной и двойной точностью).

Стандартная система команд МП содержит команды для выполнения различных логических операций над отдельными битами слов или других адресуемых единиц. Такие команды предназначены для обработки символьных и логических данных.

Минимальный набор поддерживаемых логических операций – НЕ, И, ИЛИ и сложение по модулю 2.

В дополнение к побитовым логическим