Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 962

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

внешние;

внутренние.

Внешниепрерывания. Вызываются асинхронными событиями, которые происходят вне прерываемой программы. Например, прерывания от таймера или подсистемы ввода/вывода.

Внутренниепрерывания. Вызываются событиями, которые связаны с работой процессора и являются синхронными с его операциями. Например:

арифметическое переполнение, попытка деления на 0, переполнение или исчезновение порядка при выполнении операций с плавающей запятой;

внутренние прерывания происходят при обращении к защищенным или несуществующим ячейкам памяти, а также к отсутствующему сегменту или странице;

прерывания вызывает попытка использовать незадействованный код операции, а также попытка использовать привилегированные команды в пользовательском режиме;

внутренние прерывания могут вызываться также сбоями системы, например, ошибкой четности;

при выполнении специальных команд.

Прерывание программы не должно оказывать на прерванную программу никакого влияния кроме увеличения времени ее выполнения за счет приостановки на время выполнения подпрограммы обработки прерывания. Для этого после приема запроса

на прерывание состояние МП необходимо сохранить. Для того чтобы прерванная программа могла быть продолжена после обслуживания очередного запроса на прерывание с того места, на котором она была приостановлена, состояние процессора должно быть восстановлено. Всякий раз, когда процессор воспринимает запрос на прерывание, он активизирует процедуру обслуживания, передавая ее стартовый адрес в программный счетчик. Чтобы не потерялось старое содержимое программного счетчика, которое является адресом возврата в прерванную программу, оно должно быть автоматически сохранено. Лучше всего для этой цели использовать системный стек, тогда возврат к прерванной программе будет заключаться в передаче управления по адресу, находящемуся на вершине стека. Обычно аппаратными средствами обработки прерывания автоматически сохраняется не только содержимое программного счетчика, но и регистра состояния процессора, а также его программно-доступных регистров.

Таким образом, хотя существует несколько различных способов обработки прерывания, следующая последовательность действий присуща большинству микропроцессорных систем:

фиксируются характеристики произошедшего прерывания (тип прерывания);

сохраняется состояние прерванной программы – состояние процессора;

анализируется тип прерывания и передается управление соответствующей подпрограмме обработки этого прерывания;

обрабатывается прерывание – выполняется соответствующая подпрограмма;

восстанавливается состояние процессора, что приводит к возобновлению выполнения прерванной программы.

Во всех системах прерываний предусмотрен механизм программно-управляемой блокировки запросов, который реализуется с помощью набора флажков, разрешающих или запрещающих восприятие запросов на прерывание процессором. Эти флажки образуют маску прерываний и либо упаковываются в отдельный регистр маски прерываний, либо входят в состав регистра флагов (признаков) процессора.

Существуют две системы прерываний:

радиальная система прерываний;

векторная система прерываний.

29.Радиальная система прерываний.

Физический интерфейс простейшей системы прерываний может быть представлен единственной линией запроса на прерывание IRQ (Interrupt ReQuest). Для программиста такая система прерываний представляется в виде отдельной точки входа в процедуру обслуживания.

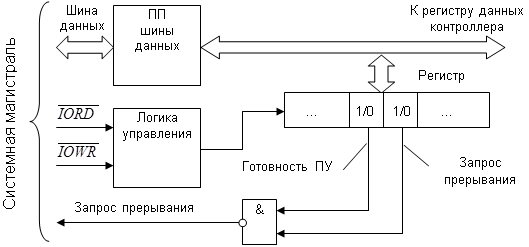

Формирование запросов на прерывание – запросов ПУ на обслуживание – происходит в контроллерах соответствующих ПУ (рис. 39).

Рисунок 39 – Формирование запроса прерывания в контроллере ПУ

Рисунок 39 – Формирование запроса прерывания в контроллере ПУВ простейших случаях в качестве сигнала запроса прерывания может использоваться сигналготовностиПУ, поступающий из контроллера ПУ с выхода соответствующего разряда регистра состояния. Однако такое простое решение обладает существенным недостатком – процессор не имеет возможности управлять прерываниями, т.е. разрешать или запрещать их для отдельных ПУ. В результате организация обмена данными в режиме прерывания с несколькими ПУ существенно усложняется. Поэтому регистр состояния контроллера ПУ дополняют еще одним разрядом – разрешениепрерывания. Запись 1 или 0 в этот разряд регистра состояния производится программным путем

(прямой вывод) по одной из линий шины данных системной магистрали.

Управляющий сигнал запроспрерыванияот ПУ формируется с помощью схемы совпадения только при наличии единиц в

разрядахготовностьПУ и разрешениепрерываниярегистра состояния контроллера ПУ.

При необходимости обслуживания нескольких ПУ в такой системе сигналы запросов на прерывание от всех ПУ поступают на один вход процессора, при этом запросы объединяются по схеме «монтажное ИЛИ». В этом случае возникает проблема идентификации ПУ, запросившего обслуживания. Данная проблема решается с помощью специальной процедуры, называемой поллингом. Функция поллинга состоит в последовательном опросе состояния всех ПУ и выявлении готовых к обслуживанию. В данном случае поллинг реализуется программнымспособомпутем анализа разряда готовности регистров состояния контроллеров ПУ. Организация прерываний с программным опросом готовности предполагает наличие в памяти микропроцессорной системы единойподпрограммыобслуживанияпрерыванийотвсехПУ. Обслуживание ПУ с помощью единой подпрограммы обработки прерываний производится следующим образом. После выполнения очередной команды основной программы процессор

проверяет