Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 1030

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

Обычно адресация основной памяти производится с точностью до байта. С целью ускорения этого процесса при обращении к основной памяти запись и считывание нескольких байтов могут осуществляться за один раз.

Основную память образуют запоминающие устройства с произвольным доступом. Основная память может включать в себя два типа устройств: оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ).

Особенностью современной ОП является ее блочная организация.

Необходимость объединения нескольких микросхем памяти возникает по двум причинам:

-

разрядность ячеек в микросхемах памяти, как правило, меньше разрядности шины данных МПС; -

емкость основной памяти современных МПС слишком велика, чтобы ее можно было реализовать на базе единственной интегральной микросхемы памяти.

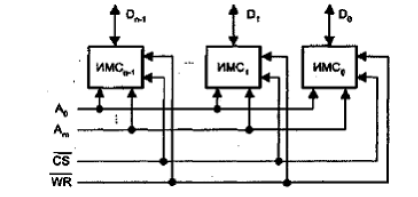

Получение требуемой разрядности ЗУ реализуется за счет объединения адресных входов объединяемых микросхем памяти. Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 24).

Рисунок 24 – Получение требуемой разрядности ЗУ

Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность. Один или несколько модулей образуют банк памяти.

Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости. В общем случае основная память МПС практически всегда имеет блочную структуру, т. е. содержит несколько банков.

При использовании блочной памяти, состоящей из B банков, адрес ячейки A преобразуется в пару (b, w), где b – номер банка, w – адрес ячейки внутри банка.

Известны три схемы распределения адресов A по банкам памяти (распределения разрядов адреса A между b и w):

-

блочная – номер банка b определяют старшие разряды адреса A; -

циклическая – b = A mod B (остаток от деления), w = A div B (частное от деления); -

блочно-циклическая – комбинация первых двух схем.

Рассмотрение основных структур блочной ОП будем проводить на примере памяти емкостью 512 слов, построенной из четырех банков по 128 слов в каждом.

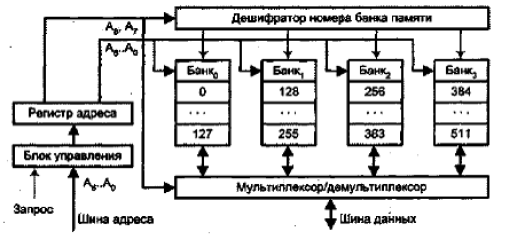

Блочная структура (схема). Адресное пространство памяти разбивается на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти (рис. 25). Для обращения к ОП используется 9-разрядный адрес, семь младших разрядов которого (А6-А0) поступают параллельно на все банки памяти и выбирают в каждом из них одну ячейку. Два старших разряда адреса (A8, А7) содержат номер банка. Выбор банка обеспечивается либо с помощью дешифратора номера банка памяти, либо путем мультиплексирования информации (на рис. 25 показаны оба варианта). В функциональном отношении такая ОП может рассматриваться как единое ЗУ, емкость которого равна суммарной емкости составляющих банков, а быстродействие – быстродействию отдельного банка.

Рисунок 25 – Структура основной памяти на основе блочной схемы

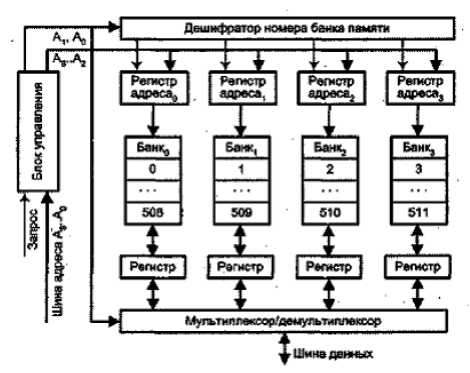

Циклическая схема. Кроме возможности наращивания емкости, блочное построение памяти обладает еще одним достоинством – позволяет сократить время доступа к данным. Это возможно благодаря потенциальному параллелизму, присущему блочной организации. Большей скорости доступа можно достичь за счет одновременного доступа к нескольким банкам памяти. Одна из используемых для этого методик называется расслоением памяти. В ее основе лежит так называемое чередование адресов (address interleaving). Прием чередования адресов базируется на рассмотренном ранее свойстве локальности по обращению, согласно которому последовательный доступ в память обычно производится к ячейкам, имеющим смежные адреса. Суть процедуры чередования адресов состоит в том, что соседние адреса относятся к разным банкам. Чередование адресов обеспечивается за счет использования для распределения адресов между банками памяти циклической схемы. В нашем примере (рис. 26) для выбора банка используются два младших разряда адреса (A1, A0), а для выбора ячейки в банке – 7 старших разрядов (A8-A2).

Рисунок 26 – Структура основной памяти на основе циклической схемы

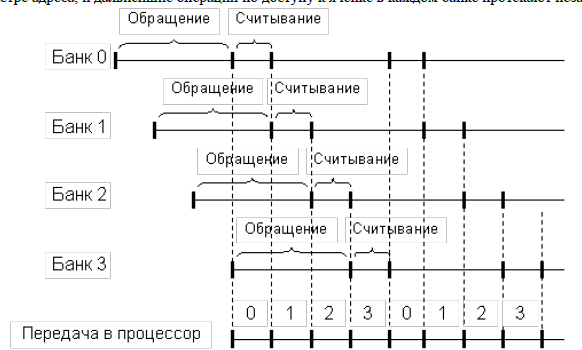

Поскольку в каждом такте на шине адреса может присутствовать адрес только одной ячейки, параллельное обращение к нескольким банкам невозможно, однако оно может быть организовано со сдвигом на один такт. Адрес ячейки запоминается в индивидуальном регистре адреса, и дальнейшие операции по доступу к ячейке в каждом банке протекают независимо (рис. 27).

Рисунок 27 – Организация обращения к основной памяти на основе циклической схемы

При большом количестве банков среднее время доступа к ОП сокращается почти в В раз (В – количество банков), но при условии, что ячейки, к которым производится последовательное обращение, относятся к разным банкам. Если же запросы к одному и тому же банку следуют друг за другом, каждый следующий запрос должен ожидать завершения обслуживания предыдущего. Такая ситуация называется конфликтом по доступу. При частом возникновении конфликтов по доступу метод становится неэффективным.

Обычно B равно 2-16, но в некоторых случаях число банков памяти может достигать 64-128.

Механизм расслоения памяти может использоваться и для повышения надежности памяти. При неисправностях или повреждениях соответствующие банки памяти исключаются из основной памяти с последующим ее перегруппированием, в результате чего работоспособность памяти сохраняется, хотя и с некоторым ухудшением ее параметров.

20. Кэш-память. Принципы кэширования памяти.

Кэш-память предназначена для повышения быстродействия процесса обращения к основной памяти.

Основная память, как правило, реализуется на относительно медленной и дешевой динамической памяти (DRAM), обращение к которой приводит к простою процессора – появляются такты ожидания. Статическая память (SRAM), построенная, как и процессор, на триггерных ячейках, имеет быстродействие, соизмеримое с быстродействием процессора, и способна сделать ненужными такты ожидания или сократить их количество, но имеет высокую стоимость. Разумным компромиссом для построения экономичных и производительных МПС является иерархический способ организации основной памяти. Идея заключается в сочетании основной памяти большого объема на DRAM с относительно небольшой буферной памятью на основе быстродействующей SRAM, т.е. в использовании двухуровневой памяти, когда между ОП и процессором размещается небольшая, но быстродействующая буферная память. В процессе работы в буферную память копируются те участки ОП, к которым производится обращение со стороны процессора. Производится отображение участков ОП на буферную память и переадресация на нее всех обращений в пределах скопированного участка. Выигрыш в быстродействии достигается за счет ранее рассмотренного свойства локальности.

Для обозначения рассмотренной буферной памяти получил распространение термин кэш-память (от английского слова cache – убежище, тайный склад, тайник, заначка), поскольку такая память обычно скрыта от программиста в том смысле, что он не может ее адресовать и может даже вообще не знать о ее существовании.

Кэш является дополнительным быстродействующим хранилищем копий блоков информации из основной памяти, вероятность обращения к которым в ближайшее время велика. Кэш не может хранить копию всей основной памяти, поскольку его объем во много раз меньше основной памяти. Он хранит только ограниченное количество блоков данных. Кроме того, кэшироваться может не вся память, доступная процессору.

Для современных микропроцессоров особенно важно то, что кэш-память (поскольку она небольшого размера) можно разместить внутри кристалла

, благодаря чему исчезают потери времени на передачу данных между процессором и памятью.

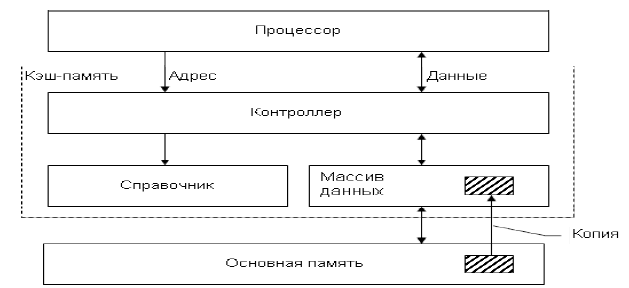

Кэш-память состоит из (рис. 28): массива данных, справочника или каталога (cache directory) и контроллера (устройства управления).

Рисунок 28 – Структура кэш-памяти

В массив данных копируются блоки основной памяти, а их адреса заносятся в каталог. Каталог содержит список текущего соответствия блоков данных областям основной памяти. При каждом обращении к памяти контроллер кэш-памяти по каталогу проверяет, есть ли действительная копия затребованных данных в кэше. Если она там есть, то реализуется кэш-попадание (cache hit), и данные берутся из кэш-памяти. Если действительной копии там нет, то реализуется кэш-промах (cache miss), и данные берутся из основной памяти и помещаются в кэш-память.

ОП состоит из 2n адресуемых слов, где каждое слово имеет уникальный n-разрядный адрес. При взаимодействии с кэшем эта память рассматривается как M блоков фиксированной длины по k слов в каждом (M = 2n/k). Кэш-память состоит из m блоков аналогичного размера (блоки в кэш-памяти принято называть строками), причем их число значительно меньше числа блоков в основной памяти (m << M). При считывании слова из какого-либо блока ОП этот блок копируется в одну из строк кэша. Поскольку число блоков ОП больше числа строк, отдельная строка не может быть выделена постоянно одному и тому же блоку ОП.

С каждой строкой кэша связана информация об адресе скопированного в нее блока основной памяти и ее состоянии. Информация о том, какой именно блок основной памяти занимает данную строку называется тегом (tag) и хранится в связанной с данной строкой ячейке памяти тегов. В качестве тега обычно используется часть адреса ОП. Здесь же хранится и информация о состоянии строки. Строка может быть действительной (valid), если в ней в текущий момент времени хранится (присутствует) копия соответствующего блока основной памяти, или недействительной. Строка может достоверно отражать соответствующий блок основной памяти или быть модифицированной (говорят строка «грязная» – dirty). Таким образом, кроме адресной части тега с каждой строкой кэша связаны биты признаков действительности (присутствия) V и модифицированности M данных. Память тегов представляет собой каталог или справочник кэш-памяти. В операциях обмена с основной памятью строка участвует целиком. Такой кэш называется