Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 967

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

(РОН1) * (РОН2) --> РОН1;

(РОН1) * (РОН2) --> РОН2;

(РОН) * (Память) --> РОН;

(РОН) * (Память) --> Память.

К достоинствам регистровой архитектуры следует отнести: компактность получаемого кода, высокую скорость вычислений за счет замены обращений к основной памяти на обращения к быстрым регистрам. С другой стороны, данная архитектура требует

более длинных инструкций по сравнению с аккумуляторной архитектурой. В целом регистровая архитектура имеет более высокую эффективность, поэтому именно она в основном используется в современных универсальных микропроцессорах.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. В английской транскрипции данную архитектуру называют Load/Storearchitecture. Команда load(загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра). Пересылка информации в противоположном направлении производится командой store(сохранение). Операнды во всех командах обработки информации в АЛУ могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения). Результат операции также заносится в регистр. В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. Допускается наличие в наборе команд ограниченного числа команд, где операнд является частью кода команды.

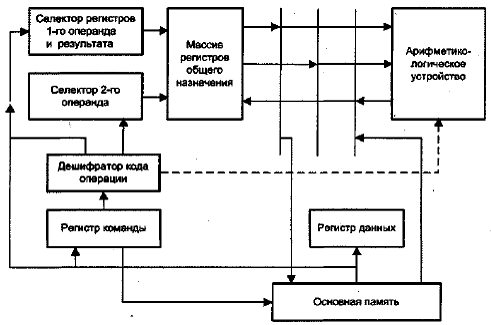

Состав и информационные тракты микропроцессора с выделенным доступом к памяти показаны на рис. 51. Две из трех шин, расположенных между массивом РОН и АЛУ, обеспечивают передачу в арифметико-логическое

устройство операндов, хранящихся в двух регистрах общего назначения. Третья служит для занесения результата в выделенный для этого регистр. Эти же шины позволяют загрузить в регистры содержимое ячеек основной памяти и сохранить в основной памяти информацию, находящуюся в РОН.

Рисунок 51 – Архитектура микропроцессора с выделенным доступом к памяти

Рисунок 51 – Архитектура микропроцессора с выделенным доступом к памятиК достоинствам архитектуры с выделенным доступом к памяти следует отнести простоту декодирования и исполнения команды. Архитектура с выделенным доступом к памяти характерна для всех микропроцессоров с RISC-архитектурой

35.Стековая архитектура микропроцессоров.

Данная архитектура основана на базе стека (стековой памяти). При соответствующем расположении операндов в стеке можно вычислять выражения полностью безадресными командами, указывающими только вид операции. Операнды перед обработкой помещаются в две верхних ячейки стековой памяти. Команда извлекает из стека в соответствии с кодом операции один или два операнда, выполняет над ними предписанную операцию и заносит результат обратно в стек. Микропроцессоры, в которых реализована архитектура на базе стека, обычно называют стековымимикропроцессорами.

При описании вычислений с использованием стека обычно используется форма записи математических выражений, известная как обратная польская запись (обратная польская нотация), которую предложил польский математик Я. Лукашевич. Особенность ее в том, что в выражении отсутствуют скобки, а знак операции располагается не между операндами, а следует за ними (постфиксная форма). Запись математических выражений с использованием обратной польской нотации производится по следующему правилу. Исходное выражение просматривается слева направо и последовательно друг за другом выписываются

встречающиеся операнды. Как только все операнды некоторой операции выписаны, записывается знак этой операции и продолжается запись операндов.

Если операндом некоторой операции является результат предыдущей операции и ее знак выписан, считается что этот операнд выписан.

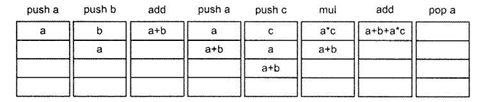

Принцип действия стекового процессора поясним на примере вычисления выражения a = a + b + a × c. Это выражение в польской записи имеет вид: а = ab+acx+. Данная форма записи не содержит скобок и однозначно определяет порядок загрузки операндов в стек и порядок выполнения операций (рис. 52), т.е. может рассматриваться как программа вычисления исходного математического выражения, если под буквами понимать команды загрузки соответствующих операндов в стек (такие команды содержат только адрес операнда в основной памяти), а под знаками операций — безадресные команды, содержащие только коды операций. Эти безадресные команды инициируют извлечение из стека двух (или одного) операндов, выполнение над ними указанной в команде операции и засылку результата в вершину стека.

Рисунок 52 – Последовательность вычислений в микропроцессоре

Рисунок 52 – Последовательность вычислений в микропроцессоре