Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 952

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

30. Векторная система прерываний.

Повышение эффективности системы прерываний связано с передачей функции идентификации ПУ, запросившего обслуживания, внешним по отношению к процессору средствам. В векторнойсистемепрерыванийПУ, запросившее обслуживание, само идентифицирует себя с помощью векторапрерывания, который принимается МП. В общем случае для передачи вектора прерывания необходима специальная шина. Однако она, как правило, физически совмещается с шиной данных системной магистрали, при этом ввод вектора прерывания осуществляется в специальном цикле магистрали, который называется цикломподтвержденияпрерывания. Такое совмещение требует включения в шину управления линии подтверждения прерывания INTA, по которой передается сигнал от процессора, разрешающий выдачу вектора прерывания в ответ на запрос прерывания от ПУ. МП, получив вектор прерывания, сразу переключается на выполнение требуемой подпрограммы обработки прерывания. Так же как и радиальная система, векторная система прерываний предполагает наличие для каждого ПУ собственной подпрограммы обработки прерывания. При этом вектор прерывания определяет, какой подпрограмме обработки прерывания процессор должен

передать управление.

Вектор прерывания может представлять собой:

полную команду вызова подпрограммы вместе с адресом подпрограммы обработки прерывания;

адрес подпрограммы обработки прерывания;

указатель на адрес подпрограммы обработки прерывания. В качестве указатель может использоваться либо адрес, по которому в памяти хранится адрес подпрограммы обработки прерывания (иногда такой указатель называют адресом вектора прерывания), либо тип прерывания.

Существует два подхода к построению векторной системы прерываний, которые различаются используемым методом формирования вектора прерывания. Первый подход использует метод децентрализованного управления – определение запроса с наибольшим приоритетом и формирование вектора прерывания осуществляется непосредственно ПУ. Второй подход использует метод централизованного управления и состоит в передаче функции формирования вектора прерывания специальному устройству – контроллеру прерывания.

Приформированиивекторапрерываниясредствами ПУлогика работы программного поллинга переносится на аппаратные средства – определение наиболее приоритетного запроса осуществляется с помощью аппаратного опроса готовности

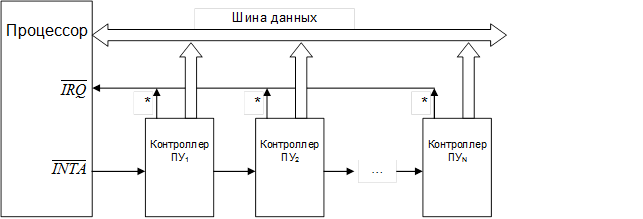

ПУ. Такой подход называется аппаратнымполлингом. Линии запросов от всех ПУ объединяются по схеме «монтажное ИЛИ» и подключаются к общей линии запроса прерывания IRQ процессора (рис. 40).

Рисунок 40 – Формирование вектора прерывания средствами ПУ

Рисунок 40 – Формирование вектора прерывания средствами ПУПроцессор при поступлении в него по линии IRQ запроса прерывания формирует управляющий сигнал подтверждения прерывания INTA, который поступает сначала в контроллер ближайшего к процессору ПУ. Если это ПУ не требовало обслуживания, то его контроллер пропускает сигнал подтверждения прерывания на следующий контроллер, иначе дальнейшее распространение сигнала прекращается и контроллер выдает в шину данных вектор прерывания. Такая схема носит ярко выраженный шлейфовый характер. Одна линия подтверждения прерывания проходит последовательно через контроллеры ПУ и образует последовательную приоритетную структуру, называемую дейзи-цепочкой. Приоритет определяется физическим положением каждого ПУ. Ближайшее к процессору ПУ имеет наибольший приоритет.

Дейзи-цепочка имеет два преимущества. Во-первых, в системной магистрали нужна только одна линия запроса прерывания (одна

линия запроса используется и в системе с программным опросом готовности ПУ, однако аппаратный опрос готовности ПУ производится гораздо быстрее). Во-вторых, в систему можно ввести новое ПУ с любым требуемым приоритетом, просто подключая его в нужную физическую позицию. Количество ПУ в системе ограничивается только числом векторов прерываний. Однако дейзи-цепочка медленнее параллельного способа, реализуемого в контроллере прерываний, так как сигнал подтверждения прерывания последовательно распространяется через каждое ПУ. Еще один недостаток шлейфовой структуры – трудность управления приоритетами. ПУ, стоящие в дейзи-цепочке ближе к процессору, обладают более высоким приоритетом, поэтому изменение приоритетов требует изменения последовательности включения ПУ, что во многих случаях затруднительно. Наиболее эффективно векторная система прерываний реализуется с помощью контроллера прерываний (рис. 41)

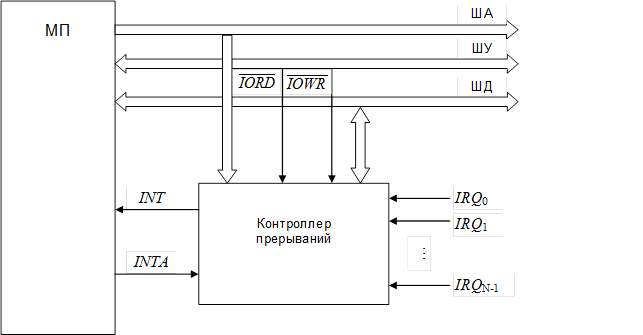

Рисунок 41 – Векторная система прерываний на основе контроллера прерываний

Рисунок 41 – Векторная система прерываний на основе контроллера прерыванийКонтроллерпрерываний(КПР) может рассматриваться как расширение процессора, по этой причине его иногда называют сопроцессором обработки прерываний.

На основе КПР формируется многоуровневая приоритетная система векторных прерываний. КПР обеспечивает прием и обработку N запросов на прерывание. Приоритетная логика КПР выбирает из числа поступивших запросов на прерывание запрос с наивысшим приоритетом и сравнивает его с текущим приоритетом запроса, находящегося на обслуживании. При превышении текущего приоритета КПР генерирует сигнал запроса прерывания INT, который поступает в процессор. МП подтверждает прием запроса INT генерацией сигнала подтверждение прерывания INTA, в ответ на который КПР выдает на шину данных системной магистрали соответствующий вектор прерывания. До тех пор, пока некоторый запрос находится в обслуживании, все запросы с равным или меньшим приоритетом игнорируются. В то же время запросы с более высоким приоритетом приводят к генерации сигнала INT, инициируя вложенные прерывания. Для оперативного управления работой контроллера предусматривается возможность его программирования, что позволяет динамически изменять приоритеты запросов, формируемые вектора прерываний и т.п.