Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 958

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

Таким образом, один из операндов всегда находится в аккумуляторе. Для выполнения операции в АЛУ производится считывание второго операнда из памяти в регистр данных. Выходы регистра данных и аккумулятора подключаются к соответствующим входам АЛУ. По окончании предписанной операции результат с выхода АЛУ заносится в аккумулятор. В процессорах аккумуляторного типа возможен следующий способ передачи данных:

(Акк) * (Память) --> Акк;

Поскольку положение одного из операндов предопределено, в командах обработки достаточно явно указать местоположение только второго операнда, т.е. команды являются одноадреснымии имеют следующий формат (рис. 48): поле кодаоперациии поле адресаячейкипамяти.

Достоинствами аккумуляторной архитектуры можно считать короткие команды и простоту декодирования команд. Однако наличие всего одного регистра порождает многократные обращения к основной памяти.

Рассмотренная

архитектура в основном используется в 8-разрядных микропроцессорах, микроконтроллерах и специализированных микропроцессорах.

33.Регистровая архитектура микропроцессоров.

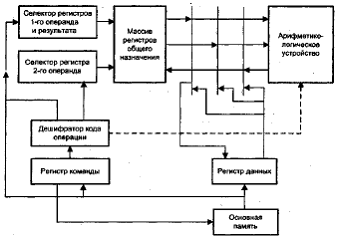

Микропроцессор с архитектурой данного типа включает в себя массив регистров (регистровый файл), известных как регистрыобщегоназначения(РОН). В микропроцессоре отсутствует специальный регистр данных, выполняющий функции аккумулятора. Функции аккумулятора выполняет один из регистров общего назначения (рис. 49).

Рисунок 49 – Архитектура микропроцессора на базе регистров общего назначения

Рисунок 49 – Архитектура микропроцессора на базе регистров общего назначенияРазмер регистров обычно фиксирован и совпадает с размером машинного слова. К любому регистру можно обратиться, указав его номер. Количество РОН в архитектурах типа CISC обычно невелико (от 8 до 32), и для представления номера конкретного регистра необходимо не более пяти разрядов, благодаря чему в адресной части команд обработки допустимо одновременно указать номера двух регистров или номер регистра и адрес памяти. RISC-архитектура предполагает использование существенно большего числа РОН (до нескольких сотен). Однако типичная для таких микропроцессоров длина команды (обычно 32 разряда) позволяет определить в команде до трех

регистров (двух регистров операндов и регистра результата).

Регистровая архитектура допускает расположение операндов в одном из двух пространств: основной памяти или регистрах. С учетом возможного размещения операндов в рамках регистровых архитектур выделяют три типа команд обработки:

-регистр-регистр;

-регистр-память;

-память-память.

В варианте «регистр-регистр» операнды могут находиться только в регистрах. В них же засылается и результат. Вариант

«регистр-память» предполагает, что один из операндов размещается в регистре, а второй в основной памяти. Результат обычно замещает один из операндов. В командах типа «память-память» оба операнда хранятся в основной памяти. Результат заносится в память. Вариант «регистр-регистр» является основным в микропроцессорах типа RISC. Команды типа «регистр-память» характерны для CISC-микропроцессоров. Ввариант «память-память» считается неэффективным, и в микропроцессорах не используется.

Операции загрузки регистров из памяти и сохранения содержимого регистров в памяти идентичны таким же операциям с аккумулятором. Отличие состоит в этапе выбора нужного регистра, обеспечиваемого соответствующими селекторами. При этом между АЛУ и регистровым файлом

должны быть, по крайней мере, три шины.

Выполнение операции в АЛУ включает в себя:

-выбор регистра первого операнда;

-определение расположения второго операнда (память или регистр);

-подачу на вход АЛУ операндов и выполнение операции;

-выбор расположения результата и занесение в него результата операции из АЛУ.

В качестве двух операндов, поступающих в АЛУ, могут использоваться операнды, хранящиеся в любых РОН, или одним из операндов может быть операнд, считываемый из основной памяти. Результат операции, выданный АЛУ, записывается в РОН или в основную память.

При адресации в команде, выполняющей операцию в АЛУ, указываются два адреса операндов, т.е. команды являются

двухадресными(рис. 50).

Обычно первый адрес указывает только на регистр общего назначения, а второй адрес может указывать как на регистр общего назначения, так и на основную память. Результат операции обычно записывается по первому адресу, однако более удобной считается система, позволяющая выборочно производить запись как по первому, так и по второму адресу.