Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 971

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

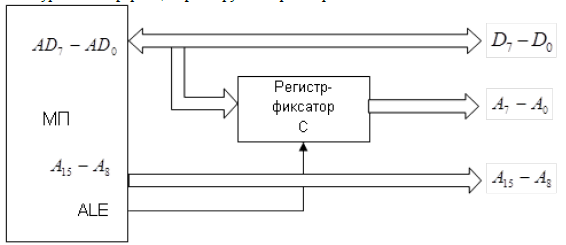

50.Организация параллельной передачи данных.

Входящий в состав шины управления сигнал ALE используется для разделения функций, выполняемых совмещенной шиной AD. По этому сигналу присутствующая на шине AD адресная информация должна быть принята (зафиксирована) во внешний (по отношению к МП) адресный регистр-фиксатор. Для этой цели обычно служит срез сигнала ALE (переход из высокого уровня в низкий). Обычно каждый модуль микропроцессорной системы с двухшинной магистралью (модуль памяти или интерфейс периферийного устройства) содержит локальный адресный регистр для запоминания адресной информации. Для фиксации адресной информации может быть использован и один общий регистр, в результате МП с двухшинной магистралью преобразуется в МП с тремя раздельными шинами (рис. 16). Когда уровень управляющего сигнала, приходящего на вход C регистра-фиксатора, становится высоким, входная информация без изменения передается на выход. При переходе управляющего сигнала на входе C в низкий уровень информация фиксируется в регистре.

Рисунок 16 – МПС с двухшинной магистралью

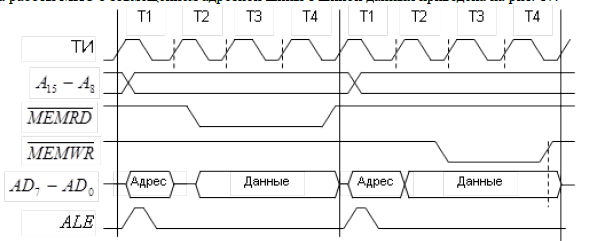

Временная диаграмма работы МПС с совмещением адресной шины с шиной данных приведена на рис. 17.

Рисунок 17 – Цикл магистрали с совмещенными шинами передачи адреса и данных

В течение первого такта T1 по совмещенной шине AD7-AD0 передаются адресные разряды A7-A0. Эти разряды по сигналу ALE фиксируются в регистре фиксаторе, который находится вне МП.

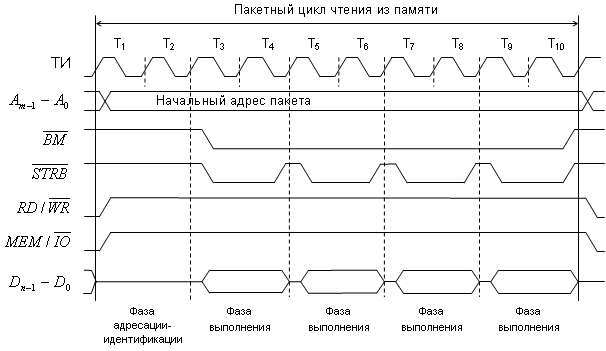

14. Механизм пакетной передачи данных по системной магистрали.

Для обслуживания некоторых внутренних запросов при работе с памятью процессору может понадобиться последовательность циклов обмена, во время которых передаются данные, расположенные в смежной области адресного пространства. Такая ситуация может иметь место при выборке операндов

, имеющих разрядность большую, чем разрядность шины данных (например, 32-разрядный процессор может обращаться к 64- или 128-разрядным операндам), или при заполнении строки кэш-памяти (например, если строка кэша имеет длину 32 байта, то для ее пересылки требуется четыре 64-разрядных цикла магистрали). Во всех таких случаях, когда требуется больше одного цикла для передачи данных, микропроцессор может выполнять пакетные циклы. Во время пакетного цикла между МП и памятью передается более одного слова, причем эти слова занимают смежные адреса и направление передачи для всех слов одинаково (т.е. все слова читаются из памяти или записываются в память). Такой блок данных называется пакетом, а протокол обмена по магистрали – режимом пакетной передачи (пакетный режим – Burst Mode).

Выполнение стандартного цикла магистрали можно разбить на две фазы:

• фаза адресации, которая включает адресацию памяти и коммутацию направления передачи;

• фаза данных, которая включает передачу данных и их фиксацию.

В пакетном режиме одна фаза адресации сопровождается множественными фазами данных (чтения или записи, но не чередующимися). Это означает, что пакет данных передается без указания текущего адреса внутри пакета. При этом передается адрес только первого слова, все последующие адреса генерируются из первого в самой памяти по определенному, заранее известному правилу. Такой протокол обмена возможен, если адрес и сигналы идентификации типа цикла выдавать только в первой фазе пакета, а в каждой из последующих фаз передавать только данные, адреса для которых уже не передаются по адресной шине. В результате на передачу первого слова затрачивается две фазы, а далее данные передаются в каждой фазе, а не через фазу, как в обычных циклах обмена.

На рис. 21 приведена временная диаграмма пакетного цикла чтения из памяти, включающего передачу четырех слов.

Рисунок 21 – Пакетный цикл чтения из памяти

Рисунок 21 – Пакетный цикл чтения из памяти В пакетном цикле фаза 1 занимает такты T1 и T2, а фаза 2 – такты T3 и T4. Пакетный цикл начинается МП так же, как и обычный: в первой фазе на шине адреса устанавливается адрес первого слова пакета, а на шине управления – сигналы идентификации типа цикла (например, MEM/IO и RD/WR). В следующей фазе передается первое слово данных, и, если оно не единственное, специальный управляющий сигнал BM,

который указывает, что данный цикл пакетный. Далее МП продолжает цикл как пакетный, не вводя фазы адресации, а сразу перейдет к передаче следующего слова данных. О завершении пакетного цикла микропроцессор сообщает памяти снятием сигнала BM.

Скорость передачи собственно данных в пакетном режиме увеличивается естественным образом за счет уменьшения числа передаваемых адресов. Из рис. 21 видно, что для передачи четырех слов с помощью пакетного цикла требуется 10 тактов, в то время как передача четырех слов с помощью обычных циклов занимает 4 цикла х 4 такта = 16 тактов.

15. Архитектура подсистемы памяти микропроцессорной системы. Характеристики подсистемы памяти микропроцессорной системы

Подсистема памяти – совокупность устройств, служащих для запоминания, хранения и выдачи информации, представленной в виде цифровых кодов.

Содержимое памяти обычно относится к одной из четырех категорий:

• коды программы;

• данные (постоянные);

• промежуточные результаты обработки (переменные);

• состояние системы.

Можно выделить три основные функции памяти:

• хранение программ и данных;

• запоминание промежуточных результатов, используемых в ходе обработки;

• работа в качестве элемента устройства обработки.

Отдельные устройства, входящие в подсистему памяти микропроцессорной системы, называют запоминающими устройствами (ЗУ) или памятями того или иного типа. Оба эти термина в настоящее время почти синонимы. ЗУ обычно употребляется, когда речь идет о принципе построения некоторого устройства памяти. Например, полупроводниковое ЗУ, ЗУ на магнитных дисках и т.п. Термин память употребляется, когда хотят подчеркнуть выполняемую устройством памяти логическую функцию или место в составе системы. Например, основная память, кэш-память, внешняя память.

Основные операции в памяти:

• занесение информации в память – запись;

• выборка информации из памяти – считывание или чтение.

Обе эти операции называют обращением к памяти или обращением при считывании (чтении) и обращением при записи.

Характеристики запоминающих устройств внутренней памяти

Основными характеристиками запоминающих устройств являются:

• емкость;

• единица пересылки;

• метод доступа;

• быстродействие;

• стоимость.

Емкость (объем) ЗУ определяется максимальным количеством информации, которое одновременно может в нем храниться, и выражается в количестве слов определенной разрядности – битов, байтов или n-разрядных слов. Так как эта емкость может быть достаточно велика, то обычно используют более крупные единицы, образованные присоединением приставок К/K (кило/kilo), М/M (мега/mega), Г/G (гига/giga), Т/T (тера/tera), П/P (пета/peta), Е/E (экса/exa), З/Z (зетта/zetta), И/Y (иотта/yotta) к перечисленным выше единицам. В вычислительной технике эти приставки означают умножение основной единицы измерений на целую степень числа 2:

• K – 210 = 1024;

• M – 220 = 1 048 676;

• G – 230 = 1 073 741 824;

• T – 240 = 1 099 511 627 776;

• P – 250;

• E – 260;

• Z – 270;

• Y – 280.

Важной характеристикой ЗУ является единица пересылки. Для основной памяти единица пересылки определяется шириной шины данных, т.е. количеством битов, передаваемых по линиям шины параллельно (одновременно). Обычно единица пересылки равна длине слова. Данные могут передаваться единицами, превышающими размер слова, которые называются блоками. Например, блоками передаются данные при пересылке между основной памятью и кэш-памятью.

При оценке быстродействия необходимо учитывать применяемый в данном типе ЗУ метод доступа к данным. Различают четыре основных метода доступа: прямой, последовательный, произвольный и ассоциативный. В ЗУ внутренней памяти используются три последних метода:

Быстродействие ЗУ является одним из важнейших его показателей. Для количественной оценки быстродействия обычно используют три параметра: время обращения к памяти, цикл обращения и скорость передачи данных.

Время обращения к памяти. Время обращения при записи и чтении определяется следующим образом

tобр зап = tд + tзап;

tобр чт = tд + tсчит,

где

• tд – время доступа.

• tзап – время записи.

• tсчит – время считывания.

Практически для большинства ЗУ tобр зап = tобр чт.

Время цикла обращения к памяти (цикла памяти) или период обращения Tц. Означает минимальное время между двумя последовательными обращениями к памяти. Период обращения включает в себя время доступа плюс некоторое дополнительное время. Дополнительное время может требоваться для приведение в исходное состояние элементов памяти, а в некоторых типах ЗУ, где считывание информации приводит к ее разрушению, – для восстановления (регенерации) считанной информации.

Скорость передачи данных. Определяется количеством данных считываемых или записываемых запоминающим устройством в единицу времени.

Стоимость ЗУ принято оценивать отношением общей стоимости ЗУ к его емкости в битах, т.е. стоимостью хранения одного бита информации.

Многоуровневая организация памяти микропроцессорной системы