Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 945

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

1. Архитектурные принципы фон Неймана.

Термин «электронная вычислительная машина – ЭВМ» определяется как совокупности технических средств, служащих для автоматизированной обработки дискретных данных по заданному алгоритму.

В основе архитектуры современных ЭВМ лежит представление алгоритма решения задачи в виде программы последовательных вычислений. Согласно стандарту ISO 2382/1-84, программа для ЭВМ – это «упорядоченная последовательность команд, подлежащая обработке».

ЭВМ, в которой определенным образом закодированные команды программы хранятся в памяти, известна под названием вычислительной машины (ВМ) с хранимой в памяти программой, а сама концепция вычислительной машины – концепции хранимой в памяти программы (концепция машины с хранимой в памяти программой).

Сущность фон-неймановской концепции вычислительной машины можно свести к четырем принципам:

1. двоичного кодирования;

2. программного управления;

3. адресности;

4. однородности памяти.

Принцип двоичного кодирования

Вся информация в вычислительной машине (как данные, так и команды) кодируется в двоичной форме и разделяется на единицы (элементы) информации, которые называются словами. Группа двоичных разрядов, составляющих слово, обрабатываются одновременно. Каждый тип информации имеет свой формат. Например, в формате данных с фиксированной запятой обычно выделяют поле знака и поле значащих разрядов.

Принцип программного управления

Порядок выполнения действий вычислительной машиной задается алгоритмом. Все действия, предусмотренные алгоритмом решения задачи, представляются в виде программы, состоящей из последовательности управляющих слов – машинных команд. Каждая команда предписывает некоторую элементарную операцию из набора операций, реализуемых вычислительной машиной, с помощью которых осуществляется обработка данных. Команды программы хранятся в последовательных ячейках памяти вычислительной машины и выполняются в естественной последовательности, т. е. в порядке их положения в программе. При необходимости, с помощью специальных команд, эта последовательность может быть изменена. Решение об изменении порядка выполнения команд программы принимается либо на основании анализа результатов предшествующих действий, либо безусловно.

В формате команды выделяются две части: операционная часть и адресная часть. В операционной части задается код операции. Код операции представляет собой указание, какая операция должна быть выполнена. Адресная часть содержит адреса объектов обработки (операндов) и результата.

Принцип адресности

Структурно память вычислительной машины состоит из пронумерованных ячеек, причем процессору в произвольный момент доступна любая ячейка. Слова информации (двоичные коды команд и данных) хранятся в ячейках памяти, а для доступа к ним используются номера соответствующих ячеек, которые называются адресами слов.

Принцип однородности памяти

Команды и данные хранятся в одной и той же памяти и внешне в памяти неразличимы, распознать их можно только по способу использования, т.е. разнотипные слова информации различаются по способу использования, но не способом кодирования. Отсутствует явное различие между командами и данными. Их идентифицируют неявным способом при выполнении операций. Так, объект, адресуемый командой перехода, определяется как команда, а операнды, с которыми имеет дело команда, определяются как данные. В свою очередь, назначение (тип) данных не является их неотъемлемой составной частью, т.е. ЭВМ безразлична к целевому назначению данных – ей все равно, какую логическую нагрузку несут обрабатываемые данные. Нет, например, никаких средств, позволяющих явно отличить набор бит, представляющих число с плавающей запятой, от набора бит, являющихся строкой символов. Назначение данных определяется логикой программы. Если машина извлекает из памяти команду сложения чисел с плавающей запятой, то предполагается, что операнды – числа с плавающей запятой, и над операндами выполняется сложение согласно правилам арифметики чисел с плавающей запятой.

2. Структура фон-неймановской вычислительной машины.

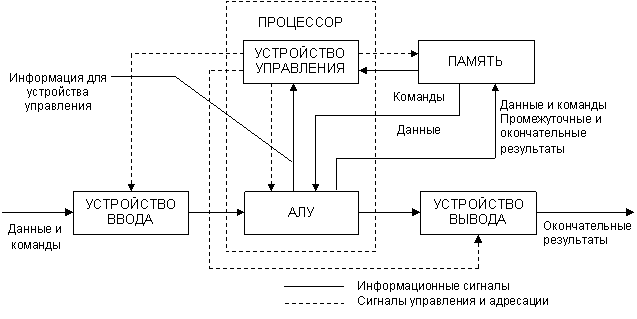

Фон-неймановская ВМ включает пять функциональных блоков (рис. 1): устройство ввода, память, АЛУ, устройство управления и устройство вывода.

Рисунок 1 - Структура фон-неймановской вычислительной машины

Рисунок 1 - Структура фон-неймановской вычислительной машины В любой ВМ имеются средства для ввода программ и данных. Информация поступает из подсоединенных к ВМ периферийных устройств (ПУ) ввода. Затем отдельные команды программы одна за другой автоматически поступают в устройство управления (УУ), которое их декодирует и управляет выполнением операции, заданной в команде. Операции обычно выполняются в арифметико-логическом устройстве (АЛУ), содержащем все необходимые для обработки данных схемы. При этом данные должны поступить в АЛУ из памяти. Результаты вычислений выводятся на периферийные устройства вывода. Связь и взаимодействие ВМ и ПУ обеспечивают порты ввода и порты вывода. Термином порт обозначают аппаратуру сопряжения периферийного устройства с ВМ. Совокупность портов ввода и вывода называют устройством ввода/вывода (УВВ). АЛУ и устройство управления вместе образуют центральное процессорное устройство (ЦПУ), которое обычно называют центральным процессором (ЦП) или просто процессором.

Чтобы программа могла выполняться, команды и данные должны располагаться в основной памяти (ОП), организованной таким образом, что каждое двоичное слово хранится в отдельной ячейке, идентифицируемой адресом, причем соседние ячейки памяти имеют следующие по порядку адреса. Доступ к любым ячейкам запоминающего устройства (ЗУ) основной памяти может производиться в произвольной последовательности. Такой вид памяти известен как память с произвольным доступом. ОП современных ВМ в основном состоит из полупроводниковых оперативные запоминающих устройств (ОЗУ), обеспечивающих как считывание, так и запись информации. Для таких ЗУ характерна энергозависимость – хранимая информация теряется при отключении электропитания. Если необходимо, чтобы часть основной памяти была энергонезависимой, в состав ОП включают постоянные запоминающие устройства (ПЗУ), также обеспечивающие произвольный доступ. Хранящаяся в ПЗУ информация в рабочем режиме ВМ может только считываться (но не записываться).

В вычислительной машине может быть дополнительная память, известная как вторичная. Введенная информация всегда сначала запоминается в основной памяти, а затем может переноситься во вторичную память для длительного хранения. Вторичная память энергонезависима и чаще всего реализуется на базе магнитных дисков. Информация в ней хранится в виде специальных программно поддерживаемых объектов – файлов.

Обработка данных осуществляется главным образом в АЛУ. Встроенные операции, как правило, элементарны: функции АЛУ обычно сводятся к простым арифметическим и логическим операциям, а также операциям сдвига. АЛУ обеспечивает обработку двух входных переменных, в результате которой формируется выходная переменная. Более сложные математические действия должны выполняться с помощью программ, использующих встроенные операции. АЛУ содержит набор регистров, используемых для промежуточного хранения информации в процессе ее обработки и называемых рабочими или регистрами общего назначения (РОН). Помимо результата операции АЛУ формирует ряд признаков результата (флагов), характеризующих полученный результат и события, произошедшие в процессе его получения (равенство нулю, знак, четность, перенос, переполнение и т. д.). Флаги могут анализироваться в УУ с целью принятия решения о дальнейшей последовательности выполнения команд программы.

Устройство управления управляет работой ВМ, организуя автоматическое выполнение программ и обеспечивая функционирование ВМ как единой системы. УУ автоматически, последовательно по одной, выбирает команды из памяти, декодирует каждую из них и генерирует необходимые для ее выполнения сигналы. Для того чтобы получить команду из памяти, УУ прежде всего должно знать ее адрес. Обычно команды выбираются из последовательных ячеек памяти, и их адреса указываются специальным программным счетчиком (program counter), находящимся в устройстве управления. После выборки текущей команды содержимое программного счетчика автоматически увеличивается с тем, чтобы указывать на следующую по порядку команду. Далее, чтобы иметь возможность декодировать и выполнить текущую команду, она помещается в регистр команд (instruction register), который находится в УУ. Код операции однозначно определяет операцию, выполняемую в процессе интерпретации команды. Адресная часть команды (если она присутствует) указывает на ячейки памяти или РОН, к которым нужно обращаться, выполняя команду (например, считывать операнды и записывать результат). Кроме того, УУ синхронизирует работу отдельных блоков ВМ. Эта функция осуществляется с помощью генератора тактовых импульсов (ГТИ), или тактового генератора.

Таким образом, функционирование ВМ сводится к выполнению последовательности команд программы.

3. Понятие организации и архитектуры.

Под организацией понимают состав компонентов (аппаратных или программных средств), связи между ними и их функциональные характеристики.

ВМ имеет многоуровневую иерархическую организацию со своими составными компонентами на каждом уровне:

-

нижний уровень – уровень физических компонентов – физическая организация (представляется в виде принципиальной схемы); -

уровень реализуемых в ВМ функций – логическая (функциональная) организация (представляется в виде функциональной схемы); -

верхний уровень – уровень аппаратуры (состав, функциональные связи и характеристики аппаратных модулей) – структурная организация (представляется в виде структурной схемы).

Определение термина «архитектура компьютера» дал в 1970 г. С.С.Хассон (S.S.Husson): это «характеристики вычислительной системы с точки зрения программиста». Первоначально под термином архитектура вычислительной машины подразумевалось описание структуры данных и регистров, необходимое для уяснения системы команд ВМ и интерпретации этих команд. Иначе говоря, этим понятием охватывались те минимальные знания, которые могли понадобиться программисту для составления программы на машинном языке:

-

программно-доступные регистры (программистская модель) ВМ; -

форма представления команд для ВМ (коды операций и форматы машинных команд) и правила их интерпретации этой машиной; -

способы адресации данных в этих командах; -

форма представления данных (типы и форматы данных).

Архитектура, понимаемая в этом смысле, называется архитектурой набора команд. Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть ВМ, которая видна программисту, разрабатывающему программы на машинно-ориентированном языке. Следует отметить, что это наиболее частое употребление этого термина.

В широком смысле под архитектурой понимают структурную организацию ВМ в виде совокупности функциональных модулей и определенных связей между ними.

Под микроархитектурой понимается структурная организация процессора (микропроцессора), т.е. внутренняя реализация архитектуры набора команд процессора.

4. Фон-неймановская (принстонская) и гарвардская архитектуры. Организация пространств памяти и ввода/вывода.

Фон-неймановская (принстонская) и гарвардская архитектуры

Эти архитектурные варианты были предложены в конце 1940-х годов специалистами соответственно Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

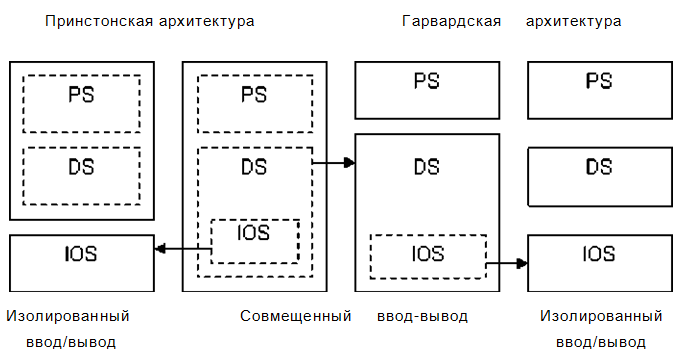

В большинстве современных ВМ для хранения программ и данных используется общая память. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Такая организация получила название архитектуры фон Неймана или Принстонской архитектуры, а ВМ с такой архитектурой называют машинами фон-неймановского или принстонского типа. В них области для хранения программ (Program Space – PS) и данных (Data Space – DS) образуют единое пространство и могут размещаться в любом месте общей памяти. При этом нет никаких признаков, указывающих на тип информации в ячейке памяти. Содержимое ячейки интерпретируется ЦП, и задача программиста – следить за тем, чтобы данные и программа обрабатывались по-разному.

Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд и данных в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема основной памяти в каждом конкретном случае применения микропроцессора. Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее классическом варианте программы и данные хранятся в двух раздельных памятях, каждая из которых соединяется с процессором отдельной шиной, что позволяет полностью совмещать во времени выборку и исполнение команд, т.е. одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. ЭВМ, спроектированные в соответствии с концепцией разделения памяти на два вида, называют машинами гарвардского типа. Такое разделение позволяет повысить быстродействие и упростить схемотехническую реализацию микропроцессорной системы.

Недостатки Гарвардской архитектуры связаны с необходимостью использования большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении различных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволяет в значительной степени преодолеть указанные недостатки.

Дальнейшее совершенствование архитектур обоих типов состояло в выделении специального пространства данных небольшого объема, которое представляет собой набор программно-доступных регистров (Register Space). В отличие от памяти и портов ввода/вывода регистры располагаются всегда внутри процессора вместе с АЛУ, что обеспечивает быстрый физический доступ к информации, хранящейся в них. В некоторые интервалы времени программа наиболее интенсивно работает лишь с небольшим объемом данных. Для временного хранения этих данных и предназначена регистровая область – набор программно доступных регистров. Регистровая область может быть как полностью изолирована от пространства данных DS, так и частично пересекаться с ним, что дает возможность рассматривать отдельные регистры процессора как обычные ячейки памяти данных. Такая организация является целесообразной, если в процессоре поддерживается быстрый доступ ко всей или хотя бы к некоторой части памяти данных.

Пространство ввода/вывода представляет набор адресуемых буферных схем и регистров, которые называются портами и через которые осуществляется связь с внешними и внутренними аппаратными средствами ВМ. В вычислительной машине может использоваться два варианта организации доступа к портам ввода/вывода: изолированный и совмещенный ввод/вывод.

При изолированном вводе/выводе порты размещены в специальном пространстве ввода/вывода (Input/Output Space – IOS), изолированном от других пространств данных. В этом случае процессор имеет специальный набор команд ввода/вывода.

При совмещенном вводе/выводе или вводе/выводе с отображением на память изолированное пространство ввода/вывода отсутствует, а в пространстве памяти данных DS выделяются области, в которых размещаются порты. Организация доступа к портам в такой ВМ ничем не отличается от процесса обращения к данным в памяти.

На рис. 2 представлены четыре типовых набора областей для хранения программ и данных. Стрелками показан процесс изоляции отдельных областей, приводящий к появлению нового типового набора. Все наборы существуют реально, каждый имеет свои преимущества и недостатки, учет которых позволяет создавать высокоэффективные системы различного назначения.

Рисунок 2 – Типовые наборы областей для хранения программ и данных

Организация пространств памяти и ввода/вывода

Память представляет собой линейно упорядоченный набор n-разрядных ячеек с произвольным доступом (одномерный массив) – линейная память. Все ячейки пронумерованы, таким образом каждой ячейке набора соответствует число, называемое ее адресом. Все адреса занимают целочисленный диапазон от 0 до 2m-1 (m – разрядность адреса), который образует адресное пространство памяти. В большинстве случаев процессор может адресоваться к памяти с точностью до одного байта, т.е. наименьшей адресуемой единицей является байт и память имеет байтовую организацию.

Программные объекты (команды и операнды) могут иметь длину, превышающую один байт, например, два байта – 16-разрядное слово или просто слово, четыре байта – 32-разрядное слово или двойное слово, восемь байтов – 64-разрядное слово или учетверенное слово. Такие объекты располагаются в смежных ячейках пространства памяти. Адресом объекта служит наименьший из адресов ячеек, занимаемых им. Обычно младший байт размещается в ячейке с меньшим адресом, в этом случае адресом объекта является адрес его младшего байта. Такой порядок называется Little-Endian Memory Format. Он используется в микропроцессорах с архитектурой x86 фирмы Intel. В других семействах процессоров применяют обратный порядок – Big-Endian Memory Format, в котором объекты располагаются в смежных ячейках памяти, начиная со старшего байта, а младшие байты размещаются в последующих ячейках. В этом случае адресом объекта является адрес его старшего байта. Такой порядок используется, например, в процессорах фирмы Motorola. Для взаимного преобразования форматов в процессорах имеются специальные команды. Операция обращения к памяти предполагает считывание или запись всего объекта как единого целого. Например, 16-разрядные слова в памяти хранятся в двух соседних ячейках. Старший байт слова занимает ячейку с большим адресом, а младший – ячейку с меньшим адресом. При этом адрес младшего байта служит адресом слова.

Часто организация памяти предусматривает определенные ограничения на возможное расположение многобайтовых объектов. В этом случае объекты должны выравниваться по соответствующей границе: слова по четному адресу, двойного слова по адресу, кратному четырем, учетверенного слова по адресу, кратному восьми. Например, слова в памяти могут находиться только по четным адресам. Тогда при доступе к слову значение младшего разряда его адреса, указывающего на байт в слове, во внимание не принимается. Такая память имеет границу слов.