Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 955

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

Соответствующая логика управления должна заботиться о том, чтобы своевременно переписывать заполненный буфер в ОП (например, во время свободных тактов шины). При использовании буферизации процессор полностью освобождается от работы с ОП.

Согласно методу обратнойзаписи, слово заносится только в кэш-память. Если соответствующей строки в кэш-памяти нет, то нужный блок сначала пересылается из ОП, после чего запись все равно выполняется только в кэш-память. При этом строка кэша, в которую произведена запись, помечается как грязная или модифицированная, т.е. требующая выгрузки в основную память.

Только после этой выгрузки (записи в основную память) строка становится чистой, и ее можно будет использовать для кэширования других блоков без потери целостности данных. В основную память данные переписываются только целой строкой. Выгрузка (запись) в основную память откладывается до наступления крайней

необходимости (например, обращение к кэшированной памяти другим устройством, замещение строки в кэше новыми данными) или выполняется в свободное время после модификации всей строки. Данный метод сложнее в реализации, но существенно эффективнее (в среднем на 10%), чем сквозная запись, так как позволяет уменьшить количество операций записи в основную память.

Предотвратить несогласованность в ситуации, когда в основную память из устройства ввода, минуя процессор, заносится новая информация и неверной становится копия, хранящаяся в кэш-памяти, позволяют два приема. В первом случае ввод любой информации в ОП автоматически сопровождается соответствующими изменениями в кэш-памяти. Во втором случае ввод любой информации в ОП допускается только через кэш-память.

24.Концепция виртуальной памяти.

Термин виртуальная память ассоциируется с возможностью адресовать пространство памяти, большее, чем емкость основной (реальной, физической) памяти конкретного процессора.

При выполнении программы предполагается, что все команды программы и данные содержатся в основной памяти, так как обращение к не существующим в основной памяти командам и данным невозможно. Следовательно, общее пространство памяти, к которому может обращаться программа, ограничивается емкостью основной памяти, т.е. аппаратными средствами. Однако

было бы удобнее составлять программу, не учитывая емкость основной памяти. Суть концепции виртуальной памяти заключается в том, что адреса, к которым обращается выполняющаяся программа (задача, процесс), отделяются от адресов, реально существующих в основной памяти. Те адреса, на которые делает ссылки выполняющаяся программа, называются виртуальными(логическими)адресами, а те адреса, которые существуют в основной памяти, называются реальнымиили физическими. Диапазон виртуальных адресов, к которым может обращаться выполняющаяся программа, называется пространствомвиртуальных

адресовэтойпрограммы. Диапазон физических адресов, реально существующих в основной памяти, что определяется конкретным процессором, называется пространством физическихадресовэтогопроцессора. Для программы создается единоевиртуальноеадресноепространство– виртуальная (логическая) память, в которой физическая ограниченность емкости основной памяти скрыта от нее, т.е. создается видимость произвольной адресации с отсутствием ограничения на емкость используемой памяти, что значительно облегчает программирование.

Несмотря на то, что программы обращаются к виртуальной памяти (виртуальным адресам), процессор в действительности должен работать с реальной памятью. Поэтому во время выполнения программы виртуальные адреса необходимо преобразовывать в реальные (физические), причем это нужно делать быстро, так как в противном случае производительность системы будет снижаться до неприемлемых уровней и тем самым практически сведутся на нет те преимущества, которые призвана обеспечить концепция виртуальной памяти. Соответствие между физическими и виртуальными адресами устанавливается совместно аппаратными средствами и операционной системой, причем это

делается прозрачно (невидимо) для программиста.

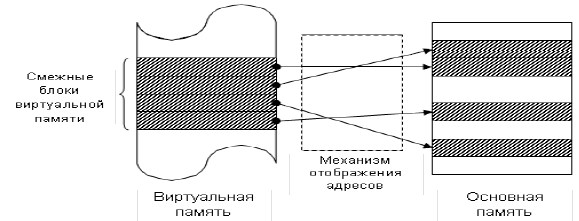

Для установления соответствия между виртуальными и физическими адресами на практике используется механизмдинамическогопреобразованияадресовDAT, который обеспечивает преобразование адресов во время выполнения программы. Этот механизм обладает следующим свойством (рис. 32): смежные адреса виртуального адресного пространства не обязательно будут смежными в физической памяти. Это свойство называют искусственнойсмежностью. Оно позволяет устранять фрагментациюфизической памяти.

Рисунок 32 – Отображение виртуальных адресов в физические

Таким образом программист освобождается от необходимости учитывать размещение своих программ и данных в физической памяти. Он получает возможность писать программы наиболее естественным образом, прорабатывая только детали алгоритма и структуры программы и игнорируя конкретные особенности структуры аппаратных средств, служащих для выполнения программы. При этом микропроцессорная система может рассматриваться только как логическое средство, обеспечивающее реализацию