Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 970

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

7.Шинная организация микропроцессорных систем: с одной шиной, с двумя видами шин, с тремя видами шин.

В микропроцессорной системе системная магистраль служит единственным трактом для потоков команд, данных и управления. Наличие общей шины существенно упрощает реализацию МПС, позволяет легко менять ее состав и конфигурацию. Вместе с тем, именно с шиной связан и основной недостаток такой архитектуры: в каждый момент передавать информацию по шине может только одно устройство. Основную нагрузку на шину создают обмены между процессором и памятью, связанные с извлечением из памяти команд и данных и записью в память результатов вычислений. На операции ввода/вывода остается лишь часть пропускной способности шины. Практика показывает, что даже при достаточно быстрой шине для 90% приложений этих остаточных ресурсов обычно не хватает, особенно в случае ввода или вывода больших массивов данных.

Поэтому при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная архитектура в чистом ее виде оказывается недостаточно эффективной. Более распространена архитектура с иерархией шин, где помимо системной шины имеется еще несколько дополнительных шин. Они могут обеспечивать непосредственную связь между устройствами с наиболее интенсивным обменом, например процессором и кэш-памятью. Другой вариант использования дополнительных шин – объединение однотипных устройств ввода/вывода с последующим выходом с дополнительной шины на системную. Это позволяет снизить нагрузку на общую шину и более эффективно расходовать ее пропускную способность. Наибольшее распространение получили микропроцессорные системы с одной шиной, с двумя или тремя видами шин.

В структурах с одной шиной имеется одна системная шина, обеспечивающая обмен информацией между процессором и памятью, а также между устройствами ввода/вывода, с одной стороны, и процессором либо памятью – с другой (рис. 8).

Рисунок 8 – МПС с одной шиной

Для такого подхода характерны простота и низкая стоимость. Однако одношинная организация не в

состоянии обеспечить высокую скорость обмена, причем узким местом является именно шина.

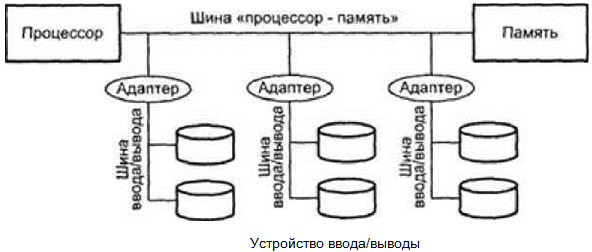

В МПС с двумя видами шин устройства ввода/вывода подключаются к шинам ввода/вывода, которые берут на себя основной обмен, не связанный с выходом на процессор или память (рис. 9). Подключение осуществляется с помощью адаптеров шин, которые обеспечивают буферизацию данных при их пересылке между системной шиной и контроллерами устройств ввода/вывода. Это позволяет микропроцессорной системе поддерживать работу множества устройств ввода/вывода и одновременно развязать обмен информацией по тракту процессор-память и обмен информацией с устройствами ввода/вывода. Подобная схема существенно снижает нагрузку на скоростную шину процессор-память и способствует повышению общей производительности микропроцессорной системы.

Рисунок 9 – МПС с двумя видами шин

Шина процессор-память обеспечивает непосредственную связь между процессором и основной памятью. В современных микропроцессорах такую шину часто называют шиной переднего плана (передней или первичной) и обозначают аббревиатурой FSB (Front-Side Bus). Интенсивный обмен между процессором и памятью требует, чтобы полоса пропускания шины, т.е. количество информации, проходящей по шине в единицу времени, была наибольшей. В варианте с одной шиной роль этой шины выполняет системная шина, однако в плане эффективности значительно выгоднее, если обмен между процессором и основной памятью ведется по отдельной шине. К рассматриваемому виду можно отнести также шину, связывающую процессор с кэш-памятью второго уровня, известную как шина заднего плана (тыльная или вторичная) – BSB (Back-Side Bus). BSB позволяет вести обмен с большей скоростью, чем FSB, и полностью реализовать возможности более скоростной кэш-памяти. Архитектура с использованием шин FSB и BSB известна как архитектура двойной независимой шины DIB (Dual Independent Bus). Наличие двух шин позволяет одновременно обращаться к основной памяти и кэш-памятью второго уровня, тем самым увеличивая общую производительность системы.

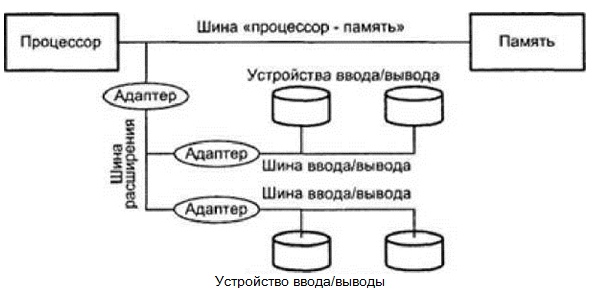

Для подключения быстродействующих периферийных устройств в систему шин может быть добавлена высокоскоростная шина расширения (рис. 10).

Рисунок 10 – МПС с тремя видами шин

Шины ввода/вывода подключаются к шине расширения, а уже с нее через адаптер к шине процессор-память. Схема еще более снижает нагрузку на шину процессор-память. Такую организацию шин называют архитектурой с «пристройкой» (mezzanine architecture).

8. Характеристики микропроцессоров.

Архитектура МП ориентирована на достижение универсальности применения, высокой производительности и технологичности.

Универсальность (возможность разнообразного применения) МП определяется их широкими функциональными возможностями и обеспечивается:

• программным управлением, позволяющим производить программную настройку МП на выполнение определенных функций;

• гибкой системой команд и разнообразием способов адресации;

• магистрально-модульным принципом построения;

• специальными аппаратно-логическими средствами: регистровая память, виртуальная память, многоуровневая система прерываний, прямой доступ к памяти и т.п.

Относительно высокая производительность МП достигается использованием для их построения быстродействующих микросхем и специальных архитектурных решений, таких как регистровая память, кэш-память, конвейерная обработка, суперскалярная архитектура, предсказание переходов, механизм динамического выполнения команд и т.п.

Технологичность микропроцессорных средств обеспечивается модульным принципом конструирования, который предполагает реализацию этих средств в виде набора функционально законченных микросхем, просто объединяемых в соответствующие устройства и системы.

Кроме перечисленных выше трех основных особенностей, исключительно широкое применение МП в различных цифровых устройствах и системах обеспечивается также:

• низкой стоимостью;

• небольшими размерами;

• малой мощностью потребления;

• высокой надежностью и большой устойчивостью к неблагоприятным внешним воздействиям.

МП характеризуется очень большим числом параметров и качеств, поскольку он, с одной стороны функционально является сложным программно-управляемым цифровым процессором, т.е. устройством ЭВМ, а с другой – интегральной микросхемой, т.е. электронным прибором. Поэтому для МП важны такие качества и параметры, как:

• тип микроэлектронной технологии, проектные нормы и число слоев металлизации (проектные нормы определяют минимальные топологические размеры элементов, что, в свою очередь, определяет количество транзисторов, размещаемых на кристалле МП, и максимальную рабочую частоту МП);

• количество кристаллов, образующих МП;

• площадь кристалла и количество транзисторов на кристалле;

• тип корпуса;

• разрядность МП;

• быстродействие МП (рабочая частота; число одновременно декодируемых инструкций; число команд, запускаемых на выполнение за один такт; время выполнения команд);

• размер адресуемой памяти;

• наличие и размер кэш-памяти;

• наличие арифметического сопроцессора;

• число входящих в микропроцессорный набор дополнительных микросхем и выполняемые ими функции;

• система команд (количество команд, выполняемые операции, способы адресации, наличие команд обработки бит, чисел с плавающей запятой, десятичной арифметики);

• форматы данных;

• типы и число уровней прерывания;

• возможность прямого доступа к памяти;

• пропускная способность интерфейса ввода/вывода (частота и разрядность системной шины);

• количество и уровни питающих напряжений;

• требования к синхронизации;

• параметры используемых сигналов;

• потребляемая мощность;

• помехоустойчивость;

• нагрузочная способность;

• надежность и т.д.

Классификация микропроцессоров.

Микропроцессоры делятся на отдельные классы в соответствии с их архитектурой, структурой и функциональным назначением.

По числу кристаллов, образующих МП, различают микропроцессоры:

• однокристальные с фиксированной разрядностью и системой команд;

• многокристальные с фиксированной разрядностью и системой команд;

• многокристальные с разрядно-модульной организацией (секционные микропрограммируемые).

По назначению различают МП:

• универсальные (общего назначения);

• специализированные.

По типу набора команд (по типу архитектуры набора команд) различают МП:

• реализованные на базе архитектуры, называемой компьютером со сложным (полным, расширенным) набором команд (CISC – Complex Instruction Set Computer) – МП с CISC-архитектурой или CISC-микропроцессоры;

• реализованные на базе архитектуры, называемой компьютером с сокращенным набором команд (RISC – Reduced Instruction Set Computer) – МП с RISC-архитектурой или RISC-микропроцессоры.

По виду обрабатываемых входных сигналов различают МП:

• цифровые;

• аналоговые.

По характеру временной организации работы