Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 1008

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

Особенность драйверов двунаправленных портов, которые не требуют инициализации, заключается в том, что при считывании возвращаемое значение равно логическому произведению сигнала на линии и содержимого одноименного разряда регистpa данных порта DPTx. По этой причине те разряды порта, которые будут считываться, должны быть предварительно установлены в 1 командой записи в порт и лишь затем прочитаны. Порты с рассматриваемой схемотехникой не имеют регистра направления передачи и, следовательно, не должны инициализироваться. При работе в режиме ввода линия имеет высокое входное сопротивление, но при чтении неподключенного входа возвращается 1.

Квазидвунаправленные драйверы отличаются от предыдущего драйвера тем, что на линии установлен внутренний подтягивающий резистор RPULLUP. Поэтому входное сопротивление линии ввода не столь велико, как в двух предыдущих случаях, т.е. входной буфер линии не эквивалентен входу логического элемента. Поэтому драйвер с рассматриваемой схемотехникой и получил название квазидвунаправленного. Линии с этим типом драйвера не требуют инициализации, но для работы в режиме ввода, так же как и в предыдущем случае, необходимо предварительно записать в соответствующий разряд регистра данных 1.

Драйверы

линий с изменяемой схемотехникой могут быть выполнены двумя способами. Однако преследуемая цель одна – сократить число навесных элементов. В первом случае драйвер каждой линии содержит подтягивающим к 1 резистор RPULLUP, который обеспечивает уровень логической единицы на входе при неподключенном выводе. Во втором случае драйвер дополнен подтягивающим к 0 резистором RPULLDOWN, который способен служить нагрузочным резистором датчика, выходной каскад которого выполнен по схеме эмиттерного повторителя.

Различают линии с нормальной и повышенной нагрузочной способностью. Если речь идет о нормальной нагрузочной способности, то следует ориентироваться на следующие цифры: Iвых0 = 1,6-2,0 мА, Iвых1 = 0,4-2,0 мА. Типовые значения повышенной нагрузочной способности: Iвых0 = Iвых1 = 25 мА. Предельное значение повышенной нагрузочной способности составляет: Iвых1 = 60 мА (Microchip PIC17). Число выводов МК с повышенной нагрузочной способностью обычно ограничено. Таймеры и процессоры событий

Модули таймера в 8-разрядных МК различных фирм имеют следующие особенности:

число каналов входного сравнения и выходного захвата (IС и ОС), которые реализованы в модуле таймера МК, может быть различно. Так, в МК Motorola семейства НС05 типовыми решениями являются модули 2IC+2OC или 1IC+1OC, и

модуль таймера в составе МК всегда только один. МК Motorola семейства НС11 имеют в своем составе модуль таймера с конфигурацией 3IC+5OC;

-

в ряде модулей каналы могут быть произвольно настроены на функцию входного захвата (IС) или выходного сравнения (ОС) при инициализации; -

счетчик модуля таймера может не иметь функции программного останова, т.е. он будет считать всегда. Поскольку в этом случае состояние счетчика нельзя синхронизировать с каким-либо моментом работы МПC, то такой счетчик характеризуют как свободно считающий (free counter); -

часто счетчик таймера не имеет опции тактирования внешним сигналом, т.е. не может работать в режиме счетчика событий.

Аппаратные средства таймера позволяют решить многие задачи управления в реальном времени. Однако процесс совершенствования алгоритмов управления предъявляет все новые требования к структуре МК. Как следствие, все более отчетливо проявляются ограничения модулей таймера:

-

недостаточное число каналов сравнения и захвата, принадлежащих одному счетчику временной базы. В результате невозможно сформировать синхронизированные между собой многоканальные импульсные последовательности; -

фиксированная конфигурация каналов (или захват или сравнение) часто не удовлетворяет пользователя; -

с использованием средств выходного сравнения возможно формирование сигнала по способу широтно-импульсной модуляции (ШИМ), однако несущая частота ШИМ сигнала тем меньше, чем больше вычислений требуется выполнять при реализации алгоритма управления и чем больше число ШИМ каналов требуется реализовать.

Следующий этап в развитии модулей подсистемы реального времени МК – модули процессоров событий.

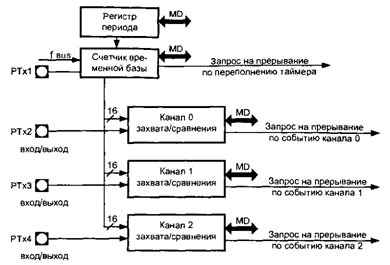

Модульпроцессорасобытий(рис. 72) содержит в себе 16-разрядный счетчик временной базы и некоторое количество универсальных каналов захвата/сравнения. Счетчик может тактироваться импульсной последовательностью с выхода программируемого делителя частоты тактирования внутренних магистралей fBUS или внешним генератором. Счетчик имеет опции пуска/останова и сброса в 0. В некоторых моделях процессора событий счетчик временной базы доступен для чтения «на лету».

Режим чтения «на лету» предусматривает автоматическое копирование содержимого старшего и младшего байтов счетчика в специальные буферные регистры в момент выполнения операции чтения любого байта счетчика (старшего или младшего). Тогда при чтении второго байта счетчика возвращается код из соответствующего буферного регистра. Тем самым исключается ошибка считывания по причине изменения состояния счетчика временной базы за время чтения. Наиболее совершенные модели процессора событий 8-разрядных МК допускают изменение коэффициента счета счетчика временной базы

.

Рисунок 72 – Структура процессора событий

Универсальные каналы захвата/сравнения в процессоре событий полностью идентичны друг другу и в зависимости от программных настроек могут работать в одном из трех режимов:

-

режим входного захвата; -

режим выходного сравнения; -

режим широтно-импульсной модуляции (ШИМ).

Первые два режима по принципу действия ничем не отличаются от аналогичных режимов модуля таймера.

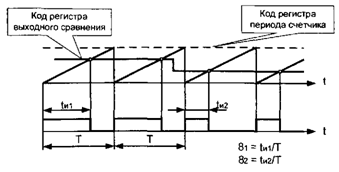

В режиме широтно-импульсной модуляции (рис. 73) на выводе PTxi МК формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса (в некоторых моделях длительность паузы) прямо пропорциональна коду в регистре данных канала. Поскольку счетчик временной базы допускает изменение коэффициента счета, то одновременно может регулироваться и период широтно-модулированной импульсной последовательности.

Рисунок 73 – Принцип работы канала захвата/сравнения в режиме ШИМ

Рисунок 73 – Принцип работы канала захвата/сравнения в режиме ШИМРежим ШИМ в различных моделях процессоров событий имеет существенные отличия. В некоторых МК код коэффициента заполнения имеет однобайтовый формат, следовательно, дискретность регулирования коэффициента