Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 996

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

Подсистема ввода/вывода отвечает за связь с устройствами ввода/вывода.

Обычно употребляется термин периферийныеустройства(ПУ), которые подразделяются на устройстваввода/вывода(УВВ – клавиатура, мышь, принтер, монитор и др.) и внешниезапоминающиеустройства(ВЗУ). Внешние запоминающие устройства занимают в микропроцессорной системе особое положение. С точки зрения выполняемой функции они относятся к подсистеме памяти (внешняя память, предназначенная для хранения информации, совместно с основной памятью может использоваться для организации виртуальной памяти), а связь с ними осуществляется так же, как и с устройствами ввода/вывода, т.е. с помощью подсистемы ввода/вывода. Поэтому при рассмотрении подсистемы ввода/вывода все периферийные устройства будем называть устройствами ввода/вывода.

Связь устройств микропроцессорной системы друг с другом осуществляется с помощью специальных совокупностей средств и правил, которые называются интерфейсами. При любой форме взаимодействия с микропроцессорной системой аппаратура ввода/вывода обычно состоит из собственно устройства ввода/вывода и устройства управления этим устройством ввода/вывода – контроллера устройства ввода/вывода. Интерфейс между процессором и контроллером устройства ввода/вывода называется системныминтерфейсом, а интерфейс между контроллером и устройством ввода/вывода

– интерфейсомввода/вывода.

Системный интерфейс, как правило, является общим для всех видов устройств ввода/вывода, а интерфейсы ввода/вывода специализированы для конкретных видов устройств ввода/вывода.

С точки зрения программиста, работающего на уровне машинных команд, подсистему ввода/вывода можно представить в виде пространства ввода/вывода IOS и набора команд ввода/вывода, обеспечивающих к нему доступ. Организация пространства ввода/вывода подобна организации пространства памяти: IOS организовано в виде набора n-разрядных ячеек – портов, каждый из которых может быть адресован независимо от других.

Между микропроцессором и периферийными устройствами происходит обмен информацией двух типов:

-

служебной; -

собственно данными.

Служебная информация от МП инициирует действия, связанные с обменом данными, и передается с помощью управляющихсловCW (Control Word). Служебные сообщения от периферийных устройств информируют МП о их текущем состоянии и называются словамисостоянияSW (Status Word). В отличие от них данные передаются с помощью словданныхDW (Data Word).

Объем служебной информации, которой обмениваются периферийные устройства и микропроцессор, а также ее интерпретация зависят от типа периферийного устройства. Для наиболее простых устройств, таких как переключатели (кнопки) или светодиодные индикаторы, служебная информация не нужна. В других случаях управляющая информация

и данные о состоянии устройства могут иметь большой объем. При этом каждое ПУ воспринимает определенный, присущий только ему набор команд управления. Поэтому передача служебной информации осуществляется путем мультиплексирования шины данных: в одни моменты времени она используется для передачи данных, в другие моменты – для передачи служебной информации. При этом для связи с периферийным устройством отводится ряд портов ввода/вывода, через которые и проходит вся информация: управляющая, слова состояния и непосредственно данные. С точки зрения программиста множество портов ввода/вывода, связанных с данным периферийным устройством, образует пространстводоступакэтомупериферийномуустройству.

Основу контроллера ПУ составляют регистры, которые служат для хранения передаваемой информации. Взаимодействие микропроцессора с этими регистрами осуществляется через порты ввода/вывода из пространства доступа к ПУ. Регистры и порты тесно связаны, иногда их трудно отделить друг от друга. Зачастую их отождествляют друг с другом. В этом смысле каждый регистр имеет свой адрес. Под адресом регистра понимается адрес порта, через который осуществляется доступ к этому регистру. В контроллере ПУ используются регистры четырех типов в зависимости от типа информации, для

хранения которой они предназначены:

-

регистр входных данных или входной регистр (доступен микропроцессору только по чтению); -

регистр выходных данных или выходной регистр (доступен микропроцессору только по записи); -

регистр состояния (доступен микропроцессору только по чтению). Содержит информацию о текущем состоянии ПУ (включено/выключено, готово/не готово к обмену данными, ошибка и т.п.); -

регистр управления (доступен микропроцессору только по записи). Служит для приема из МП команд для ПУ.

В контроллерах сложных ПУ регистров каждого типа может быть несколько. В контроллерах, предназначенных для подключения простых ПУ, удается совместить в один регистры состояния и управления, что позволяет сократить количество используемых в контроллере портов ввода/вывода, а следовательно, и адресов, выделенных для данного ПУ.

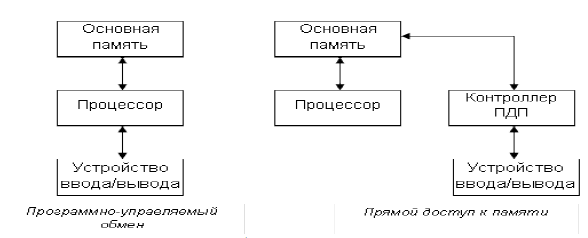

Способы организации передачи данных: прямой ввод/вывод, условный ввод/вывод, ввод/вывод по прерыванию. В микропроцессорных системах используются два основных способа организации передачи данных между системой и устройствами ввода/вывода (рис. 38):

-

программно-управляемый обмен; -

прямой доступ к памяти (ПДП). -

Программно-управляемый обмен

Рисунок 38 – Способы организации передачи данных

Программно-управляемый

обмен– это обмен, управляемый программой, т.е. когда процедуры обмена информацией с периферийным устройством инициируются и выполняются непосредственно программой, реализуемой процессором через его регистры. Программно-управляемый обмен осуществляется при непосредственном участии и под управлением процессора (см. рис. 38).

С точки зрения аппаратных затрат программно-управляемый обмен является наиболее эффективным типом обмена, поэтому он находит самое широкое применение в различных микропроцессорных системах.

Программно-управляемый обмен может осуществляться одним из трех способов:

-

прямой (безусловный, синхронный) обмен; -

условный (асинхронный) обмен (обмен по условию); -

обмен с прерыванием программы. -

В зависимости от используемого способа обмена программно-управляемый ввод/вывод называется соответственно -

прямым вводом/выводом; -

условным вводом/выводом; -

вводом/выводом по прерыванию.

Прямойввод/вывод. Использ-ся только для процессов, строго фиксированных во времени и полностью определенных. Процедуры ввода или вывода выпол-тся независимо от состояния периферийного устройства. Процедуры прямого ввода/вывода в чистом виде возможны только при работе с всегда готовыми к обмену простейшими устройствами, для которых точно известно время выполнения операции (например, индикатор). Они являются составными элементами более сложных процедур программно-управляемого обмена – условного ввода/вывода