Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 1006

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

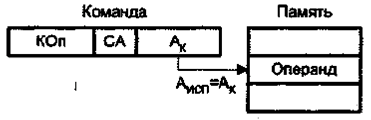

Рисунок 61 – Прямая адресация

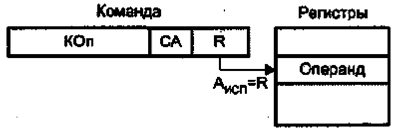

Рисунок 61 – Прямая адресацияРегистроваяадресация. Регистровая адресация напоминает прямую адресацию. Различие состоит в том, что адресное поле инструкции указывает не на ячейку памяти, а на регистр процессора (рис. 62). Обычно размер адресного поля в данном случае составляет три или четыре бита, что позволяет указать соответственно на один из 8 или 16 регистров общего назначения (РОН).

Рисунок 62 – Регистровая адресация

Двумя основными преимуществами регистровой адресации являются: короткое адресное поле в команде и исключение обращений к памяти. Малое число РОН позволяет сократить длину адресного поля команды. К сожалению, возможности по использованию регистровой адресации ограничены малым числом РОН в составе процессора.

Косвеннаярегистроваяадресация. Косвенная адресация – это такой прием, когда адресное поля команды указывает на местоположение эффективного адреса операнда. При косвенной адресации содержимое адресного поля команды

остается

неизменным, в то время как косвенный адрес в процессе выполнения программы можно изменять. Это позволяет проводить вычисления, когда адреса операндов заранее неизвестны и появляются лишь в процессе решения задачи. Дополнительно такой прием упрощает обработку массивов и списков, а также передачу параметров подпрограммам.

Косвенная регистровая адресация представляет собой вариант косвенной адресации, в котором исполнительный адрес операнда задается в регистре процессора. При этом адресное поле команды указывает на этот регистр (рис. 63).

Адресациясосмещением. При адресации со смещением исполнительный адрес формируется в результате суммирования содержимого адресного поля команды с содержимым одного или нескольких регистров процессора.

В адресном поле команды содержится константа, смысл которой в разных вариантах адресации со смещением может меняться. Константа может представлять собой некий базовый адрес, к которому добавляется хранящееся в регистре смещение. Допустим и прямо противоположный подход: базовый адрес

находится в регистре процессора, а в поле команды указывается смещение относительно этого адреса. В некоторых процессорах для реализации определенных вариантов адресации со смещением предусмотрены специальные регистры, например базовый или индексный. Использование таких регистров предполагается по умолчанию, поэтому адресная часть команды содержит только поле константы. Существуют способы, в которых смещение перед вычислением исполнительного адреса умножается на масштабный коэффициент. В наиболее общем случае адресация со смещением подразумевает наличие двух адресных полей: АК и R.

Ниже рассматриваются основные способы адресации со смещением, каждый из которых имеет собственное название.

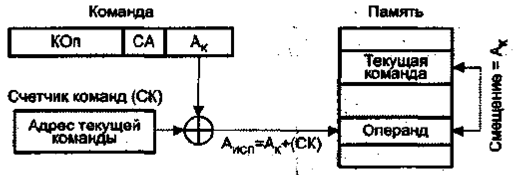

Относительнаяадресация. При относительной адресации для получения исполнительного адреса операнда содержимое подполя АК команды складывается с содержимым счетчика команд (рис. 64). Таким образом, адресный код в команде представляет собой смещение относительно адреса текущей команды. Следует отметить, что в момент вычисления исполнительного адреса операнда в счетчике команд уже сформирован адрес следующей команды, что нужно учитывать

при выборе величины смещения. Обычно поле АК трактуется как двоичное число со знаком в дополнительном коде.

Рисунок 64 – Относительная адресация

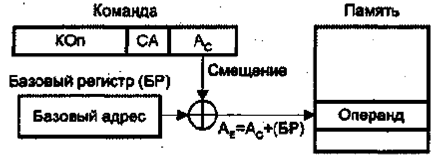

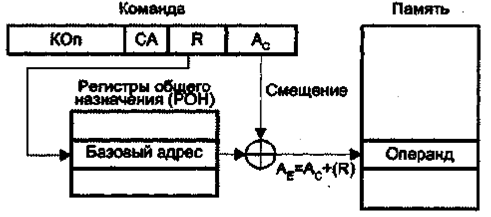

Рисунок 64 – Относительная адресацияАдресация относительно счетчика команд базируется на свойстве локальности. Это позволяет сэкономить на длине адресной части команды, поскольку разрядность поля АК может быть небольшой. Главное достоинство данного способа адресации состоит в том, что он делает программу перемещаемой в памяти: независимо от текущего расположения программы в адресном пространстве взаимное положение команды и операнда остается неизменным, поэтому адресация операнда остается корректной. Базоваяадресация. В случае базовой адресации регистр, называемый базовым, содержит полноразрядный адрес, а поле АК – смещение относительно этого адреса (рис. 65). Ссылка на базовый регистр может быть явной или неявной. В некоторых МП имеется специальный базовый регистр и его использование является неявным, т.е. адресное поле R в команде отсутствует. Более типичен случай, когда в роли базового регистра выступает один из регистров общего назначения

(РОН), тогда его номер явно указывается в поле R команды.

а – с базовым регистром

б – с использованием РОН Рисунок 65 – Базовая адресация

Базовую адресацию обычно используют для доступа к элементам массива, положение которого в памяти в процессе вычислений может меняться. В базовый регистр заносится начальный адрес массива, а адрес элемента массива указывается в подполе АК команды в виде смещения относительно начального адреса массива. Достоинство данного способа адресации в том, что смещение может иметь меньшую длину, чем полный адрес, что позволяет сократить длину адресного поля команды.

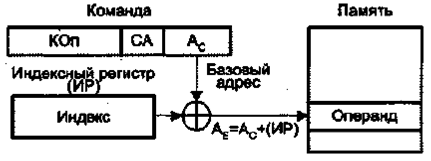

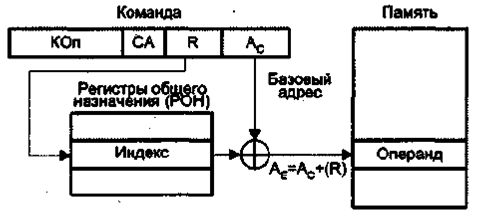

Индекснаяадресация. При индексной адресации поле АК содержит адрес памяти, а регистр, называемый индексным(указанный явно или неявно), – смещение относительно этого адреса (рис. 66).

а – с индексным регистром

б – с использованием РОН Рисунок 66 – Индексная адресация

Этот способ