Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 1016

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

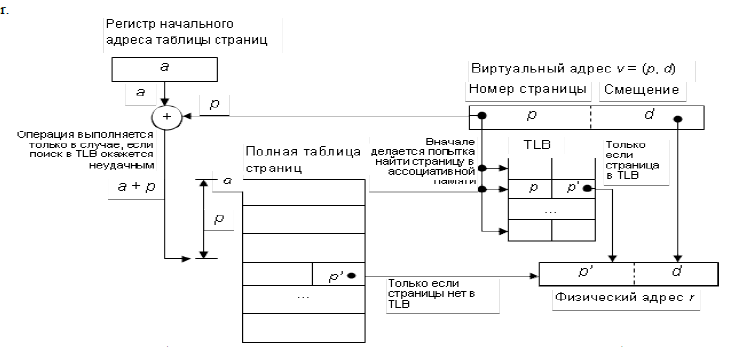

Рисунок 36 – Преобразование адресов страниц на основе ассоциативно-прямого отображения Расширение виртуального пространства влечет за собой увеличение таблицы страниц. Одним из способов решения этой проблемы является многоуровневоеразбиениенастраницы. Суть этого разбиения состоит в том, что одномерное виртуальное пространство подразделяется на два уровня – разделов и страниц, а преобразование виртуального адреса производится по

двухуровневой таблице (рис. 37). На первом уровне находится таблица разделов, которая содержит ссылки на таблицы страниц разделов. На втором уровне находятся таблицы страниц разделов. Такой подход позволяет экономить

объем памяти, выделяемый для информации отображения адресов, так как можно вести таблицы страниц не для всех разделов, в отличие от одноуровневого подхода, который требует хранения в основной памяти полной таблицы всех страниц виртуального пространства.

Рисунок 37 – Преобразование адресов страниц на основе двухуровневой схемы

26.Сегментная организация виртуальной памяти. Комбинированная сегментно- страничная организация виртуальной памяти.

В этом случае виртуальное пространство разбивается на блоки по логическим признакам, устанавливаемым программистом. Такое разбиение называется сегментацией, а блоки – сегментами. Сегменты используются для размещения логическихобъектов, например, программы (подпрограммы) или структуры данных и в отличие от страниц имеют переменную длину (размер).

Каждый сегмент может иметь именно тот размер, который необходим для размещения логического объекта. Не обязательно, чтобы все сегменты выполняющейся программы одновременно находились в основной памяти или были в ней смежными.

Программа может выполняться, если в основной памяти находится, как минимум, ее текущий сегмент.

Виртуальный адрес при

сегментной организации представляет собой упорядоченную пару v = (s, d), где s – номер сегмента, содержащего адрес v, а d – смещение адреса v относительно начала сегмента s. Динамическое преобразование адресов при сегментной организации памяти предусматривает отображение номера сегмента s на начальный (базовый) адрес сегмента As в основной памяти, т.е. номер каждого сегмента виртуального пространства ставится в соответствие положению сегмента в физическом адресном пространстве. Взаимосвязь между номерами сегментов и их базовыми адресами устанавливается таблицейсегментов. При этом полная таблица сегментов размещается в основной памяти. Преобразование адресов может выполняться практически точно так же, как и при страничной организации, за исключением того, что физический адрес получается в результате сложения базового адреса сегмента и смещения. Поскольку сегменты имеют переменную длину, смещение d необходимо контролировать, чтобы оно не выходило за пределы сегмента.

Так как сегменты являются логическими объектами, можно организовать защиту информации и управление для коллективного использования сегментированной информации, что реализуется

более естественным образом по сравнению со страничной организацией. Для этого выполняемым программам предоставляются различные сочетания прав доступа для чтения, записи и выполнения при обращении к различным сегментам.

Комбинированная сегментно-страничная организация виртуальной памяти

Виртуальный адрес представляет собой упорядоченную тройку v = (s, p, d), где s – сегмент, в котором находится виртуальный адрес v, p – страница в сегменте s, содержащая адрес v, d – смещение адреса v в странице p. Преобразование адресов осуществляется в два этапа:

-

строка таблицы сегментов указывает на таблицу страниц; -

строка таблицы страниц в свою очередь указывает на страничный кадр.

Преобразование адреса при комбинированной сегментно-страничной организации подобно на преобразование адреса при двухуровневой страничной организации. Однако эти два способа организации виртуальной памяти принципиально отличаются друг от друга. В первом случае сегменты являются самостоятельными логическими объектами. Во втором случае разбиение страниц на разделы является условным и используется для уменьшения объема памяти, требуемой для хранения информации отображения адресов.

Кроме комбинированной сегментно-страничной

организации виртуальной памяти в современных микропроцессорах используется и совместное применение сегментной и страничной организаций памяти. В этом случае сегментный и страничный механизмы работают независимо, что позволяет в свою очередь независимо управлять памятью на логическом и физическом уровнях. С помощью сегментного механизма виртуальное пространство, состоящее из сегментов, преобразуется в линейное пространство, которое затем с помощью страничного механизма путем разбиения на страницы преобразуется в физическое пространство.