Файл: Программа для эвм это упорядоченная последовательность команд, подлежащая обработке.docx

ВУЗ: Не указан

Категория: Не указан

Дисциплина: Не указана

Добавлен: 10.01.2024

Просмотров: 990

Скачиваний: 1

СОДЕРЖАНИЕ

3. Понятие организации и архитектуры.

6. Типовые структуры МПС: магистральная, магистрально-каскадная, магистрально-радиальная.

8. Характеристики микропроцессоров.

10. Циклы обращения к магистрали.

11. Организация обращения к магистрали с синхронным доступом.

12. Организация обращения к магистрали с асинхронным доступом.

14. Механизм пакетной передачи данных по системной магистрали.

16. Адресная память (запоминающие устройства с произвольным доступом).

19. Основная память: блочная, циклическая и блочно-циклическая схемы организации основной памяти.

20. Кэш-память. Принципы кэширования памяти.

22.Алгоритмы замещения информации в заполненной кэш-памяти.

23.Алгоритмы согласования содержимого кэш-памяти и основной памяти.

24.Концепция виртуальной памяти.

25.Страничная организация виртуальной памяти.

27.Архитектура подсистемы ввода/вывода микропроцессорной системы.

29.Радиальная система прерываний.

30. Векторная система прерываний.

31.Организация прямого доступа к памяти в микропроцессорной системе.

32.Аккумуляторная архитектура микропроцессоров.

33.Регистровая архитектура микропроцессоров.

34. Архитектура микропроцессоров с выделенным доступом к памяти.

35.Стековая архитектура микропроцессоров.

36.Классификация команд микропроцессоров.

37.Структура (форматы) команд микропроцессоров.

38. Регистровые структуры микропроцессоров

39. Адресация данных в микропроцессорах: представление адресной информации, способы адресации.

41.Защита памяти в микропроцессорах: механизмы защиты, концепция привилегий.

42.Поддержка операционной системы в микропроцессорах.

43.Специальные прерывания (особые случаи, исключения) в микропроцессорах.

44.Мультипрограммный режим работы микропроцессоров.

46.Резидентная (внутренняя) память микроконтроллеров.

48.Основы организации интерфейсов микропроцессорных систем.

50.Организация параллельной передачи данных.

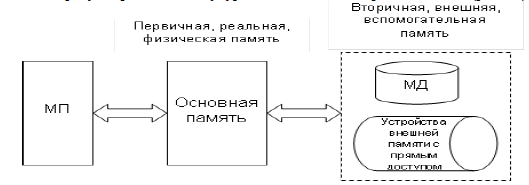

Концепция виртуальной памяти требует применения двухуровневой схемы построения памяти (рис. 33).

Рисунок 33 – Двухуровневая схема построения памяти

Первыйуровень– это основная память, в которой находятся выполняемые программы и в которой должны размещаться данные, чтобы программа во время работы могла к ним обращаться. С точки зрения виртуальной памяти это реальная или физическая память.

Второйуровень – это внешняя память большой емкости, способная хранить программы и данные, которые не могут все сразу уместиться в основной (реальной, физической) памяти ограниченной емкости. С точки зрения виртуальной памяти это вспомогательная память.

Только небольшая часть процедур и данных каждой выполняемой программы, как правило, размещается в первичной памяти одновременно. Остальная часть хранится на устройствах внешней памяти с быстрым прямым доступом. Таким образом, виртуальное адресное

пространство размещается во внешней памяти, например на магнитных дисках. Часть этого пространства, необходимая для выполнения программ в данный момент, копируется в основную память.

Виртуальнаяпамять–этоспособорганизацииосновнойпамятимикропроцессорнойсистемыбольшойемкостиспомощьювнешнейпамятиили методрасширенияадресногопространстваосновной памятизасчетеесовместногоиспользованиясвнешнейпамятью, при котором достигается гибкое динамическое распределение памяти, устраняется ее фрагментация и создаются значительные удобства для работы программистов. Это удается достигнуть без заметного снижения производительности системы ценой усложнения аппаратных средств и операционной системы и процессов их функционирования. Принцип виртуальной памяти предполагает, что пользователь при подготовке своей программы имеет дело не с физической основной памятью, действительно (реально) работающей в составе микропроцессорной системы, а с виртуальной (т.е. кажущейся) одноуровневой памятью, объем которой равен всему адресному пространству, определяемому принятым в процессоре способом адресации памяти (размером адресных

полей в форматах команд и адресных регистров).

Например, в 32-разрядных процессора фирмы Intel размер виртуального адресного пространства для одной задачи составляет 64 Тбайт.

25.Страничная организация виртуальной памяти.

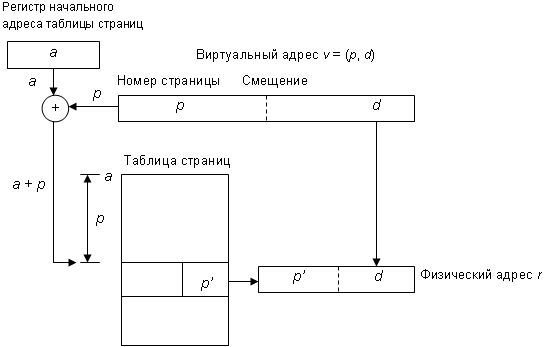

Виртуальный адрес при страничной организации – это упорядоченная пара v = (p, d), где p – номер страницы, содержащей адрес v, а d – смещение адреса v относительно начала страницы p. Основная память разделяется на страничные кадры того же самого размера, что и виртуальные страницы. Поступающая в основную память страница может быть помещена в любой свободный страничный кадр.

Динамическое преобразование адресов при страничной организации памяти предусматривает отображение номера виртуальной страницы p на номер страничного кадра основной памяти p’, т.е. номер каждой страницы виртуального пространства ставится в соответствие номеру страницы физического адресного пространства. Взаимосвязь между номерами страниц обоих типов устанавливается таблицейстраниц(рис. 35). При этом полная таблица страниц размещается в основной памяти. Прежде чем программа начинает выполняться, операционная система загружает физический адрес таблицы отображения страниц в регистр начального адреса этой таблицы. Этот базовый адрес a таблицы прибавляется к номеру страницы p, образуя адрес основной памяти a + p для строки страницы p в таблице. В

этой строке указано, что виртуальной странице p соответствует страничный кадр p’. Затем к значению p’ пристыковывается (путем конкатенации) смещение d, так что образуется физический адрес r. Такой подход называется способомпрямогоотображения, так как таблица отображения страниц содержит отдельную строку для каждой страницы виртуальной памяти

Рисунок 35 – Схема преобразования виртуального адреса в физический при страничной организации

Рисунок 35 – Схема преобразования виртуального адреса в физический при страничной организацииТак как таблица страниц ведется в основной памяти, то обращение к ней при преобразовании виртуального адреса в физический занимает относительно много времени. Для ускорения этой процедуры используется метод преобразования адресов страниц на основе ассоциативно-прямогоотображения(рис. 36). Суть этого метода состоит в использовании специального буфера – ассоциативной памяти, способной хранить небольшую часть полной таблицы отображения страниц. В этот буфер записываются номера наиболее часто используемых в данное время страниц и номера соответствующих им страничных кадров в основной памяти. В ходе преобразования адресов вначале проверяется ассоциативная память, и если